- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365968 > TSB14C01MHV IC APEX 20KE FPGA 160K 484-FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | TSB14C01MHV |

| 英文描述: | IC APEX 20KE FPGA 160K 484-FBGA |

| 中文描述: | 收發(fā)器 |

| 文件頁數(shù): | 14/35頁 |

| 文件大?。?/td> | 224K |

| 代理商: | TSB14C01MHV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

3

–

2

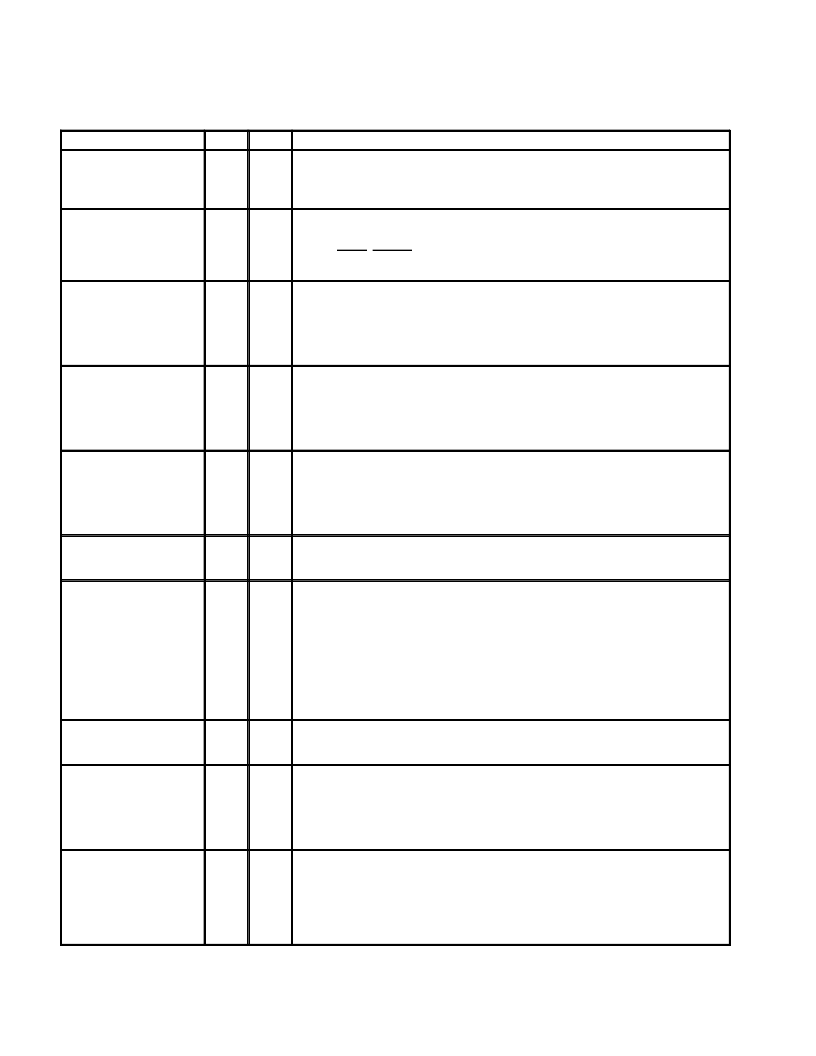

Table 3-2. Base Register Field Description (Continued)

FIELD

SIZE

TYPE

DESCRIPTION

LAST_ARB_WON_PHY_ID

6

R

Last physical layer node ID that won arbitration. This field contains the physical ID of the node

that last won the arbitration phase on the bus. This field is only valid when the E bit is 1. It is

supplied for system debug purposes. The power-up state of this field is 000000b. The state of

these bits is not affected by bus resets.

E

1

R

Enhanced register map. This bit is set to 1 to signify that additional extended registers beyond

address 0100b are implemented. When this bit is set to 1, the values in the

LAST_ARB_WON_PHY_ID, LAST_ARB_WON_PRIORITY, RDATA, RSTRB, TDATA,

TSTRB, TDOE, OCDOE fields are valid. When this bit is 0 the values in these fields are not

valid. The power-up state of this field is 1. This bit is always read in a TSB14AA1A as a 1.

RDATA

1

R

Received data line state. When the enhanced (E) bit is 1, the sampled and latched line state

read from this field is valid. This bit reads 1 for a data bit 1 (logical 1) received by the

TSB14AA1A and 0 for a data bit 0 (logical 0). The power-up state of this field is 0. This bit is

updated on a best effort basis. It is not required to be toggled with every change of its

namesake

’

s input pin. It can be expected to be updated at least every 9 SCLKs, the length of

the register read LREQ.

RSTRB

1

R

Received strobe line state. When the enhanced (E) bit is 1, the sampled and latched line state

read from this field is valid. This bit reads 1 for a strobe line 1 (logical 1)

received by the TSB14AA1A and 0 for a strobe line 0 (logical 0). The power-up state of this field

is 0. This bit is updated on a best effort basis. It is not required to be toggled with every change

of its namesake

’

s input pin. It can be expected to be updated at least every 9 SCLKs, the length

of the register read LREQ.

XFR_SPD

2

R

Transfer speed. These bits map exactly to the CLK_SEL0 and CLK_SEL1 pins (CLK_SEL0 is

the left most bit, CLK_SEL1 is the right most bit). This enables software to verify the state of

those pins and therefore the performance level of the bus transfers (100 Mbps or 50 Mbps).

See the definitions for CLK_SEL0 and CLK_SEL1 for decoding. The state of these bits is not

affected by bus resets or state machine resets. Upon power up, hardware reset, or SWHRST

reset these bits are reloaded with the values from the CLK_SEL0 and CLK_SEL1 pins.

E_REGISTER_COUNT

4

R

Enhanced register count. When the E bit is 1, this field is valid. This field is set to 0101b to

signify that there are five register addresses implemented above 0100b. The power-up state

of this field is 0101b.

PRIORITY

4

R/W

Priority setting. These bits contain the priority of the local node. These bits contain the priority

used in the arbitration process and transmitted as the PRI field in the packet header. The

power-up state of this field is 0000b. Bit field 0 maps to priority [0] the most significant bit of the

priority field used during arbitration. The hardware or SWHRST reset state of this field is the

binary state of the external priority pins on the device. The state of these bits is not affected by

bus resets or state machine resets.

When this field is nonzero TSB14AA1A uses urgent arbitration even when a fair request is

made of the PHY by the link. When this field is zero, the PHY uses fair arbitration unless the link

makes an urgent request using an 11-bit LREQ, if this device is configured to accept 11-bit

LRFQs.

PRODUCT_IDENTIFIER

4

R

Product identifier. This field contains the product identifier for the part. For the TSB14AA1A

this field should be 0000b. Bits 0-3 are used to indicate functional changes to the design. The

power-up state of this field for the TSB14AA1A is 0000b.

EBLREQ

1

R/W

Enable backplane LREQ. When this bit is set to 1, TSB14AA1A interprets all bus request

LREQs from the link as 11 bits long in the backplane format. The power-up state of this field is

0b. When this bit is set to 0, TSB14AA1A interprets the bus request LREQs as being 7 bits long

(standard cable LLC LREQs). The value of this bit must match the value of its corresponding

bit in the attached link layer or the node will not function properly. Bus reset or state machine

reset does not affect the state of this bit. This bit is cleared to 0 upon HW or SWHRST reset.

IRBR

1

R/W

Initiate robust bus reset. The IRBR bit is used when operating with 3-state transceivers to

ensure a bus reset is communicated without bus contention. It works equally well for open

collector transceivers. This bit is self-clearing. The power-up state of this field is 0b. This bit

should be used for all SW initiated bus resets. Care should be taken that when writing to the

IRBR bit, other bits in this same register are not changed. This register should be first read,

then the read value should have bit 1 (the bit to be written to the IRBR field) set to 1 and the

value written into the register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB14C01HV | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB21LV03MHV | IC APEX 20KE FPGA 200K 484-FBGA |

| TSB21LV03CHV | IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB2203X6MMX30M | IC APEX 20KE FPGA 200K 240-PQFP |

| TSB2204.5X12MMX20M | IC APEX 20KE FPGA 200K 240-PQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB14C01PM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TSB15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EURO TERMINAL BLOCKS |

| TSB150002DS | 制造商:TE Connectivity 功能描述: |

| TSB150004DS | 制造商:TE Connectivity 功能描述:Conn Europa Terminal Blocks 8 POS 13.5mm Screw ST Cable Mount 40A/Contact |

| TSB150005 | 功能描述:柵欄接線端子 5P TERM BLOCK 13.5MM 300V 40A RoHS:否 制造商:TE Connectivity / AMP 產(chǎn)品:Barrier Terminal Blocks 系列: 類型:Dual Barrier, Flat Block without Mounting Ears 節(jié)距:9.53 mm 位置/觸點(diǎn)數(shù)量:2 線規(guī)量程:22-12 電流額定值:20 A 電壓額定值:300 V 安裝風(fēng)格:Through Hole 安裝角:Vertical 端接類型:Screw 觸點(diǎn)電鍍:Tin |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。