- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365987 > TSPC106AVGS66CG MEMORY CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | TSPC106AVGS66CG |

| 英文描述: | MEMORY CONTROLLER |

| 中文描述: | 內(nèi)存控制器 |

| 文件頁(yè)數(shù): | 13/40頁(yè) |

| 文件大?。?/td> | 569K |

| 代理商: | TSPC106AVGS66CG |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

13

TSPC106

2102B

–

HIREL

–

02/02

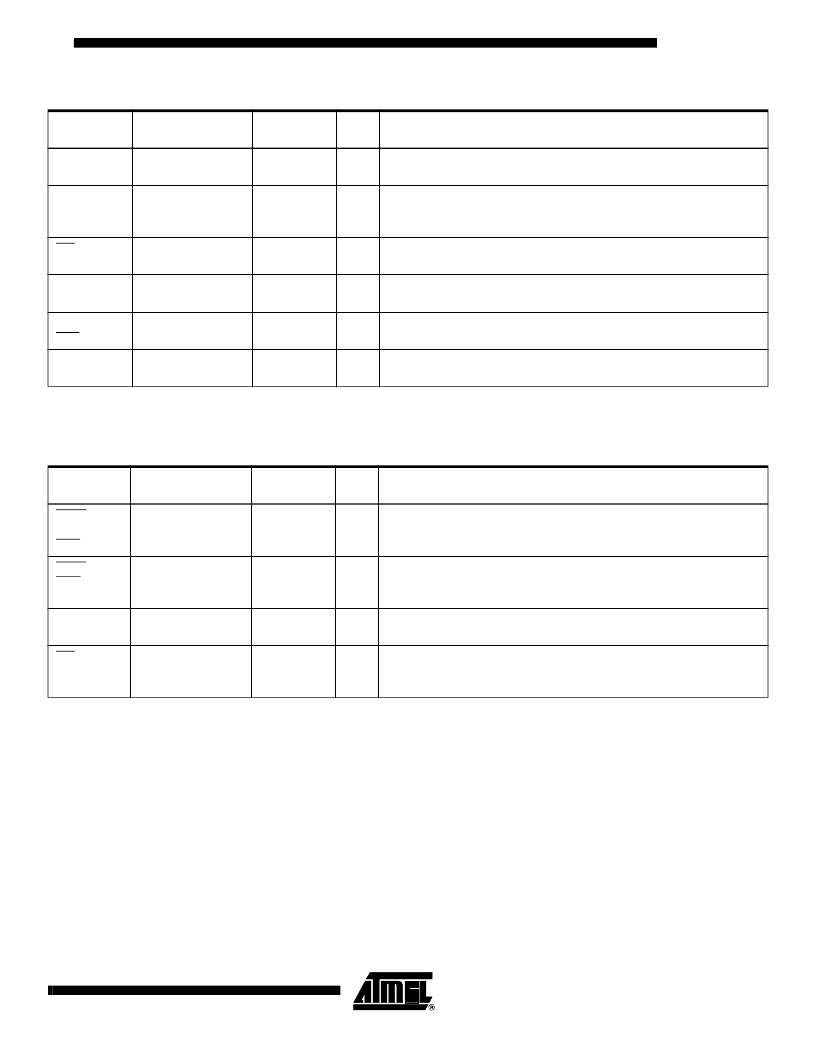

External L2 Controller Signals

When an external L2 cache controller is used instead of the internal L2 cache controller,

four signals change their functions.

DOE

DBGL2

Data RAM output

enable

1

O

Indicates that the L2 data RAMs should drive the data bus.

DWE[0:2]

DBG2

DBG3

Data RAM write

enable

3

O

Indicates that a write to the L2 data RAMs is in progress. Multiple pins

are provided to reduce loading.

HIT

Hit

1

I

Indicates that the L2 cache has detected a hit. The polarity of HIT is

programmable.

TOE

DBG1

Tag output enable

1

O

Indicates that the tag RAM should drive the L2 tag address onto the

address bus.

TV

BR2

Tag valid

1

I/O

Indicates that the current L2 cache line should be marked valid. The

polarity of TV is programmable.

TWE

BG2

Tag write enable

1

O

Indicates that the L2 tag address, valid, and dirty bits should be

updated.

Table 3.

Internal L2 Controller Signals (Continued)

Signal

Signal Name

Number of

Pins

I/O

Signal Description

Table 4.

External L2 Controller Signals

Signal

Signal Name

Number of

Pins

I/O

Signal Description

BGL2

BA1

BAA

External L2 bus

grant

1

O

Indicates that the external L2 controller has been granted mastership

of the 60x address bus.

BRL2

ADS

DALE

External L2 bus

request

1

I

Indicates that the external L2 controller requires mastership of the 60x

bus for a transaction.

DBGL2

DOE

External L2 data

bus grant

1

O

Indicates that the external L2 controller has been granted mastership

of the 60x data bus.

HIT

External L2 hit

1

I

Indicates that the current transaction is claimed by the external L2

controller. The external L2 controller will assert AACK and TA for the

transaction.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSPC106AVGS83CE | MEMORY CONTROLLER |

| TSPC106AVGS83CG | MEMORY CONTROLLER |

| TSPC106AVGSU66CE | MEMORY CONTROLLER |

| TSPC106AVGSU66CG | MEMORY CONTROLLER |

| TSPC106AVGSU83CE | MEMORY CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSPC106AVGS83CE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGS83CG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGSU/T66CE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGSU/T66CG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGSU/T83CE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。