- 您現在的位置:買賣IC網 > PDF目錄384045 > UPD72852 (NEC Corp.) MOS INTEGRATED CIRCUIT PDF資料下載

參數資料

| 型號: | UPD72852 |

| 廠商: | NEC Corp. |

| 英文描述: | MOS INTEGRATED CIRCUIT |

| 中文描述: | 馬鞍山集成電路 |

| 文件頁數: | 25/48頁 |

| 文件大小: | 249K |

| 代理商: | UPD72852 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

Data Sheet S14920EJ3V0DS

25

μ

PD72852

The bus request (ImmReq, IsoReq, PriReg, FairReq) is completed (in case of ImmReq, IsoReq, when the

subaction gap is detected) when the packet is transmitted or canceled by canceling the bus request.

(2) LREQ rules

The Link request and the status of the serial bus are asynchronous; the bus request can be canceled by the

status of the serial bus.

The following rules apply to a request by LREQ:

Link cannot issue a bus request (ImmReq, IsoReq, PriReq, FairReq) if Grant is given to an LREQ request or

until the Link’s request is canceled. The request can be canceled by the

μ

PD72852 if it detects subaction

gap at ImmReq, IsoReq.

Do not issue a RdReg or WrReg request when the status transmission is not completed by the Read request

register.

All of the bus requests (ImmReq, IsoReq, PriReq, FairReq) are canceled by a bus reset.

In addition, there is a limitation in the request of LREQ according to the state of CTL as shown in Table 4-10.

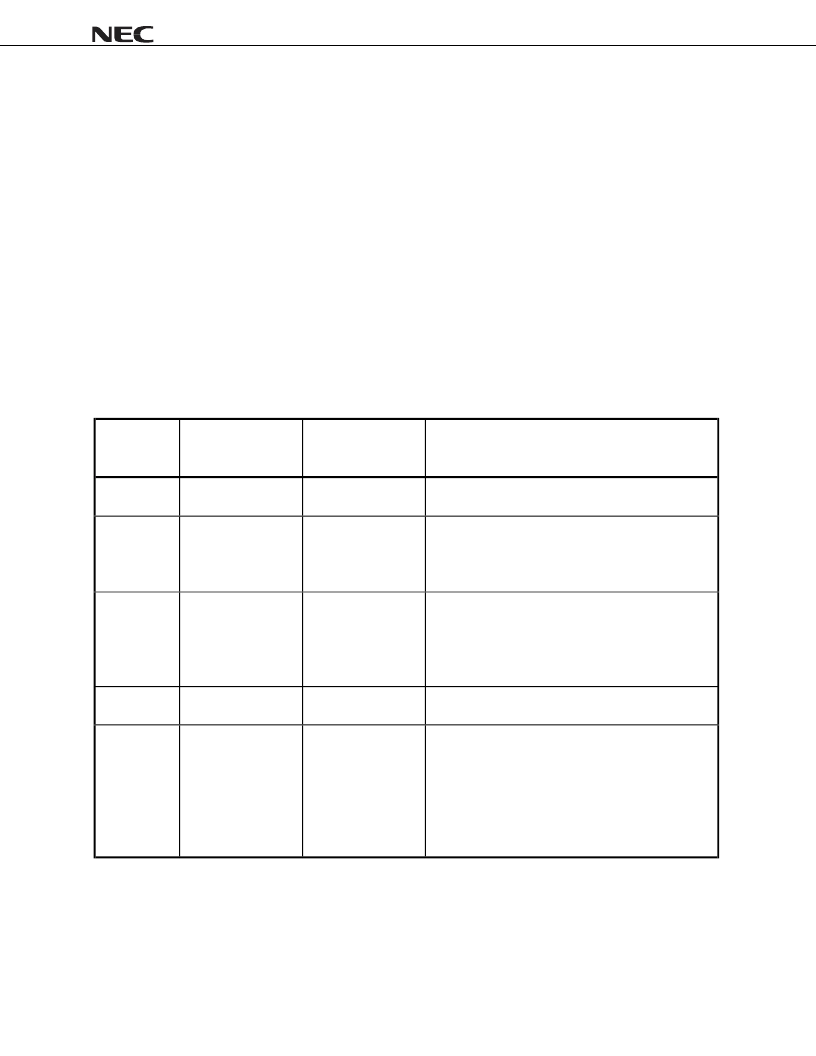

Table 4-10. Rules for Other Requests

Request

State of CTL in C

A

to

which LREQ is allowed

when PHY drives CTL

LREQ issues

permission when Link

drives CTL

Note

Fair, Priority

Idle, Status

wrong

Fair, Priority request cannot be issued until the

unprocessed bus request is completed.

Immediate

Receive, Idle

wrong

Link issues the request after completing the decoding of

Destination_ID, when the acknowledge packet is ready.

After the packet is received, it is necessary to transmit the

first bit of the request within four cycles.

Isochronous

any

correct

If the isochronous packet transmission is prepared for the

isochronous period, it is issued.

Do not issue the request to transmit the isochronous

packet appending to the currently transmitted isochronous

packet (Using Hold).

Register Read

Register Write

any

correct

Do not issue this request if the unprocessed Read request

has not been completed.

AccCtrl

any

correct

To set acceleration bit 0:

When the isochronous period starts, if the Enab_accel bit

is one, Cycle slave should adjust accelerate bit to 0.

To set acceleration bit 1:

Do not set the cycle master.

It is issued when the isochronous period ends.

相關PDF資料 |

PDF描述 |

|---|---|

| UPD72852GB-8EU | MOS INTEGRATED CIRCUIT |

| UPD72870F1 | IEEE1394 1-CHIP OHCI HOST CONTROLLER |

| UPD72870FA2 | IEEE1394 1-CHIP OHCI HOST CONTROLLER |

| UPD72871F1 | IEEE1394 1-CHIP OHCI HOST CONTROLLER |

| UPD72871FA2 | IEEE1394 1-CHIP OHCI HOST CONTROLLER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| UPD74HC04C | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD750068GT-396 | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD7507C189 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD7508CU265 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD75208 | 制造商:Panasonic Industrial Company 功能描述:IC |

發(fā)布緊急采購,3分鐘左右您將得到回復。