- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄361773 > W238-02 Clocks and Buffers PDF資料下載

參數(shù)資料

| 型號(hào): | W238-02 |

| 英文描述: | Clocks and Buffers |

| 中文描述: | 時(shí)鐘和緩沖器 |

| 文件頁(yè)數(shù): | 1/18頁(yè) |

| 文件大小: | 182K |

| 代理商: | W238-02 |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)

FTG for Integrated Core Logic with 133-MHz FSB

W238-02

Cypress Semiconductor Corporation

Document #: 38-07103 Rev. *A

3901 North First Street

San Jose

CA 95134

Revised December 26, 2002

408-943-2600

1W238-02

Features

Maximized EMI suppression using Cypress’s Spread

Spectrum technology

Low jitter and tightly controlled clock skew

Highly integrated device providing clocks required for

CPU, core logic, and SDRAM

Two copies of CPU clock at 66/100/133 MHz

Thirteen copies of SDRAM clocks at 100/133 MHz

Five copies of PCI clock compliant to PCI spec 2-1 and

capable of driving a maximum load of 40 pF

One copy of synchronous APIC clock

Two copies of 48-MHz clock (non-spread spectrum) op-

timized for USB reference input and video dot clock

Three copies of 66-MHz fixed clock

One copy of 14.31818-MHz reference clock

Power down control

SMBus interface for turning off unused clocks

Key Specifications

CPU, SDRAM Outputs Cycle-to-Cycle Jitter:.............. 250 ps

APIC, 48-MHz, 3V66, PCI Outputs

Cycle-to-Cycle Jitter:................................................... 500 ps

APIC, 48-MHz, SDRAM Output Skew:........................250 ps

CPU, 3V66 Output Skew:............................................175 ps

PCI Output Skew:........................................................500 ps

CPU to SDRAM Skew (@ 133 MHz):.........................±0.5 ns

CPU to SDRAM Skew (@ 100 MHz):.................4.5 to 5.5 ns

CPU to 3V66 Skew (@ 66 MHz): .......................7.0 to 8.0 ns

3V66 to PCI Skew (3V66 lead):..........................1.5 to 3.5 ns

PCI to APIC Skew: .....................................................±0.5 ns

Table 1. Pin Selectable Functions

Tristate#

FSEL1

0

X

0

X

1

0

1

0

1

1

1

1

FSEL0

0

1

0

1

0

1

Function

Three -State

Test

66 MHz

100 MHz

133 MHz

133 MHz

SDRAM

Three-State

Test

100 MHz

100 MHz

133 MHz

100 MHz

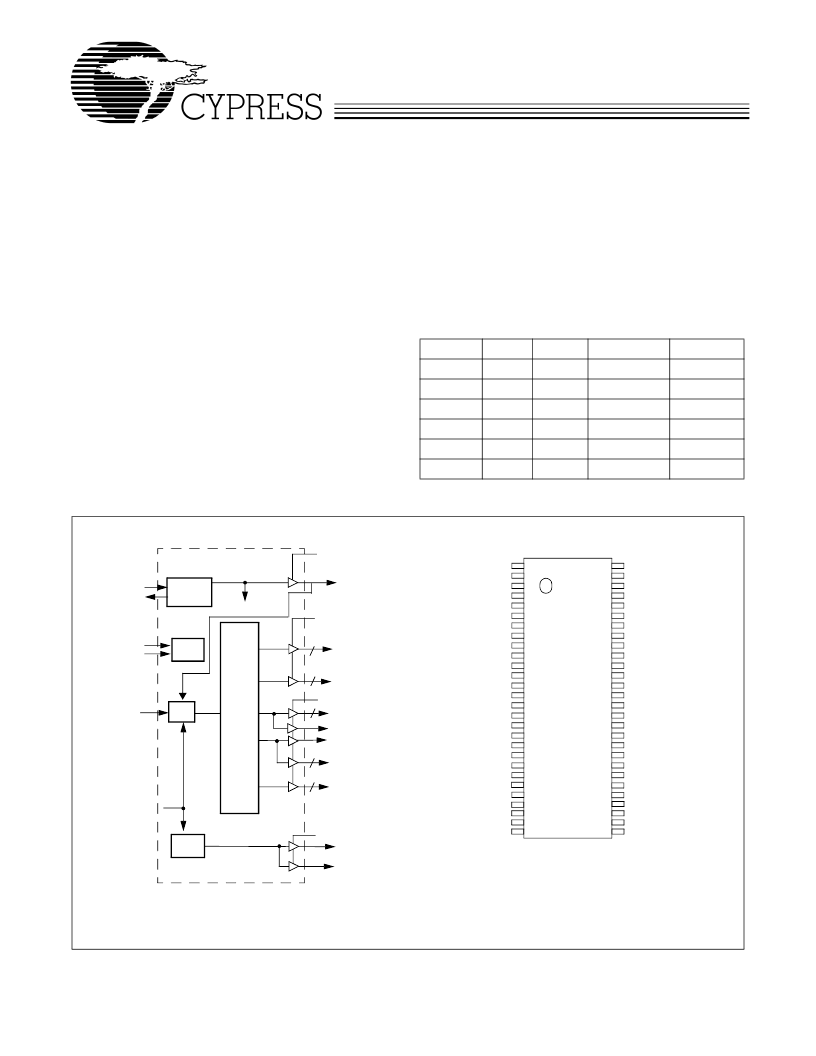

Block Diagram

Pin Configuration

VDDQ3

VDDQ2

PCI0_ICH

XTAL

OSC

PLL REF FREQ

PLL 1

X2

X1

REF/FSEL1

PCI1:4

USB

DOT

PLL2

VDDQ3

SMBus

Logic

SDATA

SCLK

3V66_0:1

CPU0:1

FSEL0:1

APIC0:1

Divider,

Delay,

and

Phase

Control

Logic

4

2

VDDQ3

2

2

SDRAM0:12

13

PWRDWN#/TRISTATE#

APIC

VDDQ2

GND

REF/FSEL1

VDDQ3

X1

X2

GND

VDDQ3

3V66_0

3V66_1

3V66_AGP

GND

PCI_ICH

PCI1

PCI2

VDDQ3

GND

PCI3

PCI4

FSEL0

GNDA

VDDA

SCLK

SDATA

GND

VDDQ3

USB

W

GND

VDDQ2

CPU0

CPU1

GND

SDRAM0

SDRAM1

VDDQ3

GND

SDRAM2

SDRAM3

SDRAM4

SDRAM5

VDDQ3

GND

SDRAM6

SDRAM7

SDRAM8

SDRAM9

VDDQ3

GND

SDRAM10

SDRAM11

VDDQ3

GND

SDRAM12

PWRDWN#/TRISTATE#

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

DOT

3V66_AGP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W238 | Clocks and Buffers |

| W23C4096-12 | x8 ROM (Mask Programmable) |

| W23C4096-15 | x8 ROM (Mask Programmable) |

| W23C4096-20 | x8 ROM (Mask Programmable) |

| W23C8192-12 | x8 ROM (Mask Programmable) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W238E32A | 制造商:OMRON INDUSTRIAL AUTOMATION 功能描述:Replaced by W238-E1-7 |

| W23C4096-12 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 ROM (Mask Programmable) |

| W23C4096-15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 ROM (Mask Programmable) |

| W23C4096-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 ROM (Mask Programmable) |

| W23C8192-12 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 ROM (Mask Programmable) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。