- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361773 > W238-02 Clocks and Buffers PDF資料下載

參數(shù)資料

| 型號(hào): | W238-02 |

| 英文描述: | Clocks and Buffers |

| 中文描述: | 時(shí)鐘和緩沖器 |

| 文件頁數(shù): | 14/18頁 |

| 文件大?。?/td> | 182K |

| 代理商: | W238-02 |

W238-02

Document #: 38-07103 Rev. *A

Page 14 of 18

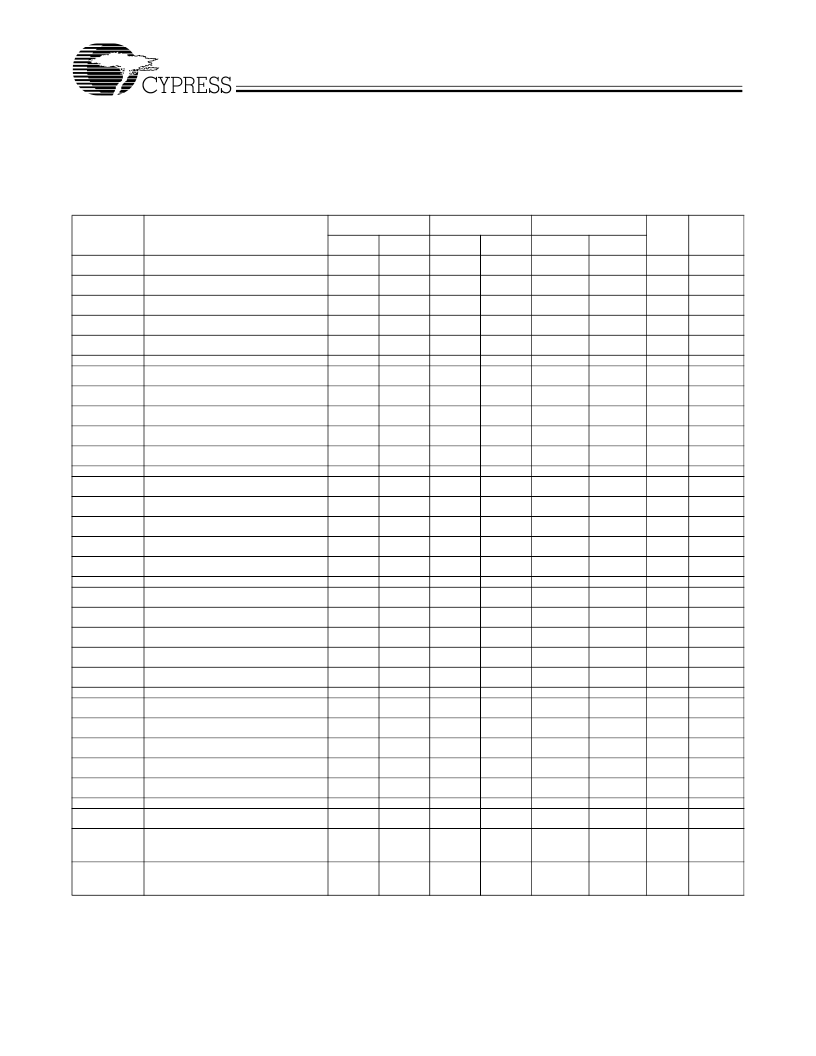

AC Electrical Characteristics

[15]

T

A

= 0°C to +70°C, V

DDQ3

= 3.3V ±5%, V

DDQ2

= 2.5V ±5%

f

XTL

= 14.31818 MHz

Spread Spectrum function turned off

AC clock parameters are tested and guaranteed over stated operating conditions using the stated lump capacitive load at the

clock output.

[17]

66.6-MHz Host

Min.

Max.

T

Period

Host/CPUCLK Period

15.0

15.5

T

HIGH

Host/CPUCLK High Time

5.2

N/A

T

LOW

Host/CPUCLK Low Time

5.0

N/A

T

RISE

Host/CPUCLK Rise Time

0.4

1.6

T

FALL

Host/CPUCLK Fall Time

0.4

1.6

Notes:

17. Period, jitter, offset, and skew measured on rising edge at 1.25 for 2.5V clocks and at 1.5V for 3.3V clocks.

18. The time specified is measured from when V

DDQ3

achieves its nominal operating level (typical condition V

DDQ3

= 3.3V) until the frequency output is stable and

operating within specification.

19. T

RISE

and T

are measured as a transition through the threshold region V

ol

= 0.4V and V

oh

= 2.0V (1 mA) JEDEC specification.

20. T

LOW

is measured at 0.4V for all outputs.

21. T

HIGH

is measured at 2.0V for 2.5V outputs, 2.4V for 3.3V outputs.

Parameter

Description

100-MHz Host

Min.

10.0

3.0

2.8

0.4

0.4

133-MHz Host

Min.

7.5

1.87

1.67

0.4

0.4

Unit

ns

ns

ns

ns

ns

Notes

17

18

19

Max.

10.5

N/A

N/A

1.6

1.6

Max.

8.0

N/A

N/A

1.6

1.6

T

Period

T

HIGH

T

LOW

T

RISE

T

FALL

SDRAM CLK Period

SDRAM CLK High Time

SDRAM CLK Low Time

SDRAM CLK Rise Time

SDRAM CLK Fall Time

10.0

3.0

2.8

0.4

0.4

10.5

N/A

N/A

1.6

1.6

10.0

3.0

2.8

0.4

0.4

10.5

N/A

N/A

1.6

1.6

10.0

3.0

2.8

0.4

0.4

10.5

N/A

N/A

1.6

1.6

ns

ns

ns

ns

ns

17

18

19

T

Period

T

HIGH

T

LOW

T

RISE

T

FALL

APIC 33-MHz CLK Period

APIC 33-MHz CLK High Time

APIC 33-MHz CLK Low Time

APIC CLK Rise Time

APIC CLK Fall Time

30.0

12.0

12.0

0.4

0.4

N/A

N/A

N/A

1.6

1.6

30.0

12.0

12.0

0.4

0.4

N/A

N/A

N/A

1.6

1.6

30.0

12.0

12.0

0.4

0.4

N/A

N/A

N/A

1.6

1.6

ns

ns

ns

ns

ns

17

18

19

T

Period

T

HIGH

T

LOW

T

RISE

T

FALL

3V66 CLK Period

3V66 CLK High Time

3V66 CLK Low Time

3V66 CLK Rise Time

3V66 CLK Fall Time

15.0

5.25

5.05

0.5

0.5

16.0

N/A

N/A

2.0

2.0

15.0

5.25

5.05

0.5

0.5

16.0

N/A

N/A

2.0

2.0

15.0

5.25

5.05

0.5

0.5

16.0

N/A

N/A

2.0

2.0

ns

ns

ns

ns

ns

17, 20

18

19

T

Period

T

HIGH

T

LOW

T

RISE

T

FALL

PCI CLK Period

PCI CLK High Time

PCI CLK Low Time

PCI CLK Rise Time

PCI CLK Fall Time

30.0

12.0

12.0

0.5

0.5

N/A

N/A

N/A

2.0

2.0

30.0

12.0

12.0

0.5

0.5

N/A

N/A

N/A

2.0

2.0

30.0

12.0

12.0

0.5

0.5

N/A

N/A

N/A

2.0

2.0

ns

ns

ns

ns

ns

17, 21

18

19

tp

ZL

, tp

ZH

tp

LZ

, tp

ZH

Output Enable Delay (All outputs)

Output Disable Delay

(All outputs)

All Clock Stabilization from

Power-Up

1.0

1.0

10.0

10.0

1.0

1.0

10.0

10.0

1.0

1.0

10.0

10.0

ns

ns

t

stable

3

3

3

ms

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W238 | Clocks and Buffers |

| W23C4096-12 | x8 ROM (Mask Programmable) |

| W23C4096-15 | x8 ROM (Mask Programmable) |

| W23C4096-20 | x8 ROM (Mask Programmable) |

| W23C8192-12 | x8 ROM (Mask Programmable) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W238E32A | 制造商:OMRON INDUSTRIAL AUTOMATION 功能描述:Replaced by W238-E1-7 |

| W23C4096-12 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 ROM (Mask Programmable) |

| W23C4096-15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 ROM (Mask Programmable) |

| W23C4096-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 ROM (Mask Programmable) |

| W23C8192-12 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 ROM (Mask Programmable) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。