- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄245649 > W3H32M64EA-533SBC (WHITE ELECTRONIC DESIGNS CORP) 32M X 64 DDR DRAM, PBGA208 PDF資料下載

參數(shù)資料

| 型號(hào): | W3H32M64EA-533SBC |

| 廠商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分類: | DRAM |

| 英文描述: | 32M X 64 DDR DRAM, PBGA208 |

| 封裝: | 16 X 20 MM, 1 MM PITCH, PLASTIC, BGA-208 |

| 文件頁(yè)數(shù): | 5/28頁(yè) |

| 文件大小: | 1057K |

| 代理商: | W3H32M64EA-533SBC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

13

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

February 2010 2010 White Electronic Designs Corp. All rights reserved

Rev. 0

ADVANCED

White Electronic Designs Corp. reserves the right to change products or specications without notice.

W3H32M64EA-XSBX

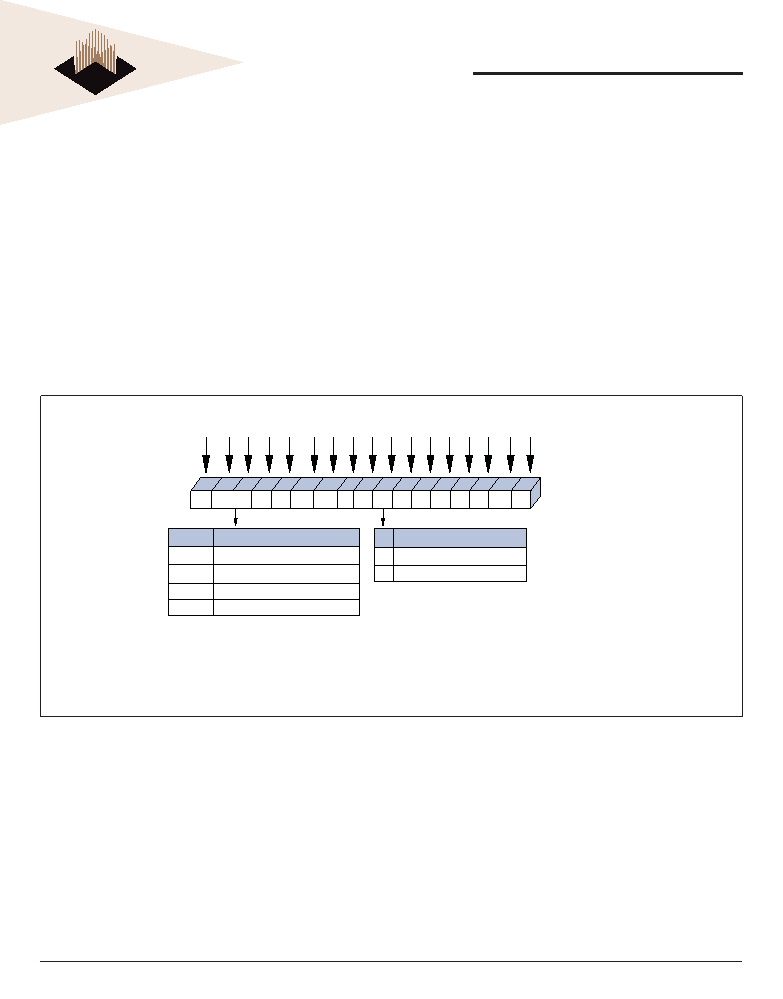

POSTED CAS ADDITIVE LATENCY (AL)

Posted CAS additive latency (AL) is supported to make

the command and data bus efficient for sustainable

bandwidths in DDR2 SDRAM. Bits E3–E5 dene the value

of AL, as shown in Figure 7. Bits E3–E5 allow the user

to program the DDR2 SDRAM with an inverse AL of 0, 1,

2, 3, or 4 clocks. Reserved states should not be used as

unknown operation or incompatibility with future versions

may result.

In this operation, the DDR2 SDRAM allows a READ or

WRITE command to be issued prior to tRCD (MIN) with

the requirement that AL ≤ tRCD (MIN). A typical application

using this feature would set AL = tRCD (MIN) - 1x tCK. The

READ or WRITE command is held for the time of the AL

before it is issued internally to the DDR2 SDRAM device.

RL is controlled by the sum of AL and CL; RL = AL+CL.

Write latency (WL) is equal to RL minus one clock; WL =

AL + CL - 1 x tCK.

A9

A7 A6 A5 A4 A3

A8

A2

A1 A0

Extended mode

register (Ex)

Address bus

97

6

5

4

3

82

1

0

A10

A12 A11

BA0

BA1

10

11

12

n

0

14

15

An

2

E14

0

1

0

1

Mode Register Set

Mode register (MR)

Extended mode register (EMR)

Extended mode register (EMR2)

Extended mode register (EMR3)

E15

0

1

MRS

0

00

00 SRT 0

00

0

BA2

1

16

0

E7

0

1

SRT Enable

1X refresh rate (0°C to 85°C)

2X refresh rate (>85°C)

FIGURE 8 – EXTENDED MODE REGISTER 2 (EMR2) DEFINITION

Notes:

1.

E16 (BA2) is only applicable for densities ≥1Gb, reserved for future use, and must be programmed to “0.”

2.

Mode bits (En) with corresponding address balls (An) greater than E12 (A12) are reserved for future use and must

be programmed to “0.”

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| WF512K32F-70G2UC5A | 512K X 32 FLASH 5V PROM MODULE, 70 ns, CQMA68 |

| WE128K32-300HQ | 512K X 8 EEPROM 5V MODULE, 300 ns, CPGA66 |

| WE128K32-300G2C | 128K X 32 EEPROM 5V MODULE, 300 ns, CQFP68 |

| WF2M32I-90HM5 | 2M X 32 FLASH 5V PROM MODULE, 90 ns, CPGA66 |

| W7NCF512H11CSAHG | 32M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W3H32M64E-ES | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:32M x 64 DDR2 SDRAM 208 PBGA Multi-Chip Package |

| W3H32M64E-ESC | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:32M x 64 DDR2 SDRAM 208 PBGA Multi-Chip Package |

| W3H32M64E-ESI | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:32M x 64 DDR2 SDRAM 208 PBGA Multi-Chip Package |

| W3H32M64E-ESM | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:32M x 64 DDR2 SDRAM 208 PBGA Multi-Chip Package |

| W3H32M64E-SB | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:32M x 64 DDR2 SDRAM 208 PBGA Multi-Chip Package |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。