- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361790 > W742E (WINBOND ELECTRONICS CORP) 4-BIT SINGLE-CHIP MICROCONTROLLER FOR SMALL GENERAL-PURPOSE INFRARED REMOTE CONTROL TRANSMITTER PDF資料下載

參數(shù)資料

| 型號(hào): | W742E |

| 廠商: | WINBOND ELECTRONICS CORP |

| 元件分類: | 4位微控制器 |

| 英文描述: | 4-BIT SINGLE-CHIP MICROCONTROLLER FOR SMALL GENERAL-PURPOSE INFRARED REMOTE CONTROL TRANSMITTER |

| 中文描述: | 4位單片機(jī)的小型通用紅外遙控器 |

| 文件頁數(shù): | 62/66頁 |

| 文件大小: | 303K |

| 代理商: | W742E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁當(dāng)前第62頁第63頁第64頁第65頁第66頁

Preliminary W742C(E)811

- 62 -

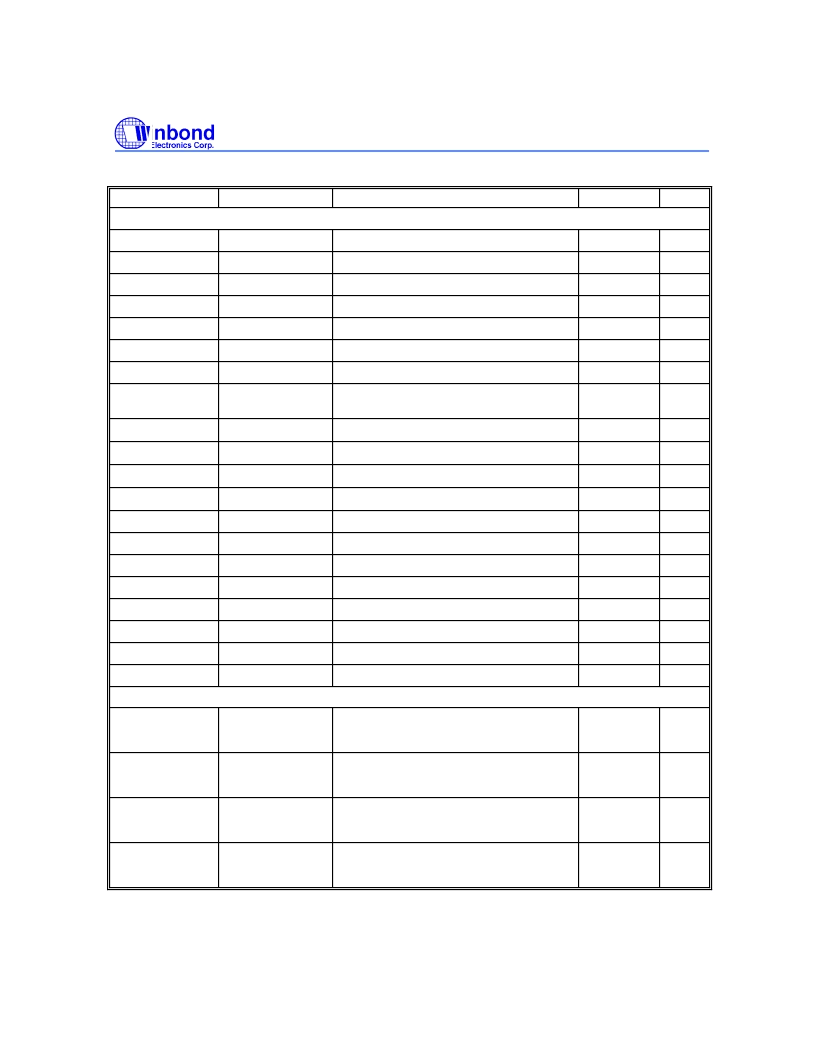

Instruction set, continued

Machine code

Flag & Register

Mnemonic

Function

Flag affected

W/C

0101 1101 0xxx xxxx

MOVA

R, EVFL

ACC, R

←

EVF.0 - EVF.3

1/1

0101 1101 1xxx xxxx

MOVA

R, EVFH

ACC, R

←

EVF.4 - EVF.7

1/1

0100 0001 iiii i iii

MOV

HEF, #I

Set/Reset HOLD mode release Enable Flag

1/1

0011 0001 0000 000 i

MOV

HEFD,#I

Set/Reset RD HOLD mode release Enable Flag

1/1

0101 0001 iiii i iii

MOV

IEF, #I

Set/Reset Interrupt Enable Flag

1/1

0100 0011 0000 iiii

MOV

PEF, #I

Set/Reset Port Enable Flag

1/1

0011 0011 0000 ii00

MOV

P1EF, #I

Set/Reset P1 Port Enable Flag

1/1

0101 0010 i iiiiiii

MOV

SEF, #I

Set/Reset STOP mode wake-up Enable Flag for

RC,RD port

1/1

0101 0100 0000 iiii

MOV

SCR, #I

SCR

←

I

1/1

0100 1111 0xxx xxxx

MOVA

R, PSR0

ACC, R

←

Port Status Register 0

ZF

1/1

0100 1111 1xxx xxxx

MOVA

R, PSR1

ACC, R

←

Port Status Register 1

ZF

1/1

0101 1111 0xxx xxxx

MOVA

R, PSR2

ACC, R

←

Port Status Register 2

ZF

1/1

0100 0010 0000 0000

CLR

PSR0

Clear Port Status Register 0

1/1

0100 0010 1000 0000

CLR

PSR1

Clear Port Status Register 1

1/1

0100 0010 1100 0000

CLR

PSR2

Clear Port Status Register 2

1/1

0101 0000 0100 0000

SET

CF

Set Carry Flag

CF

1/1

0101 0000 0000 0000

CLR

CF

Clear Carry Flag

CF

1/1

0001 0111 0000 0000

CLR

DIVR0

Clear the last 4-bit of the Divider 0

1/1

0101 0101 1000 0000

CLR

DIVR1

Clear the last 4-bit of the Divider 1

1/1

0001 0111 1000 0000

CLR

WDT

Clear WatchDog Timer

1/1

Shift & Rotate

0100 1101 0xxx xxxx

SHRC

R

ACC.n, R.n

←

(R.n+1);

ACC.3, R.3

←

0; CF

←

R.0

ZF, CF

1/1

0100 1101 1xxx xxxx

RRC

R

ACC.n, R.n

←

(R.n+1);

ACC.3, R.3

←

CF; CF

←

R.0

ZF, CF

1/1

0100 1100 0xxx xxxx

SHLC

R

ACC.n, R.n

←

(R.n-1);

ACC.0, R.0

←

0; CF

←

R.3

ZF, CF

1/1

0100 1100 1xxx xxxx

RLC

R

ACC.n, R.n

←

(R.n-1);

ACC.0, R.0

←

CF; CF

←

R.3

ZF, CF

1/1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W7700A | *****GESTRICHEN***** |

| W7700B | KLEMME FUER FLACHKABEL BIS 40 ADERN |

| W7700C | KLEMME FUER FLACHKABEL BIS 64 ADERN |

| W3435G | LEITERPLATTENSOCKEL TO18/3P 5ST |

| W3437G | LEITERPLATTENSOCKEL TO5/393P 5ST |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W742E/C811 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:4 BIT MICROCONTROLLER |

| W742E811 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| W742E813 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:4-BIT MICROCONTROLLER |

| W742E816 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| W742E81A | 制造商:WINBOND 制造商全稱:Winbond 功能描述:4-BIT MICROCONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。