- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371190 > X1228V14Z-4.5A (INTERSIL CORP) 16 Characters x 1 Lines, 5x7 Dot Matrix Character and Cursor PDF資料下載

參數(shù)資料

| 型號(hào): | X1228V14Z-4.5A |

| 廠商: | INTERSIL CORP |

| 元件分類: | XO, clock |

| 英文描述: | 16 Characters x 1 Lines, 5x7 Dot Matrix Character and Cursor |

| 中文描述: | 1 TIMER(S), REAL TIME CLOCK, PDSO14 |

| 封裝: | ROHS COMPLIANT, PLASTIC, MO-153AC, TSSOP-14 |

| 文件頁數(shù): | 14/31頁 |

| 文件大小: | 569K |

| 代理商: | X1228V14Z-4.5A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

X1228

REV 1.3 3/24/04

Characteristics subject to change without notice.

14 of 31

www.xicor.com

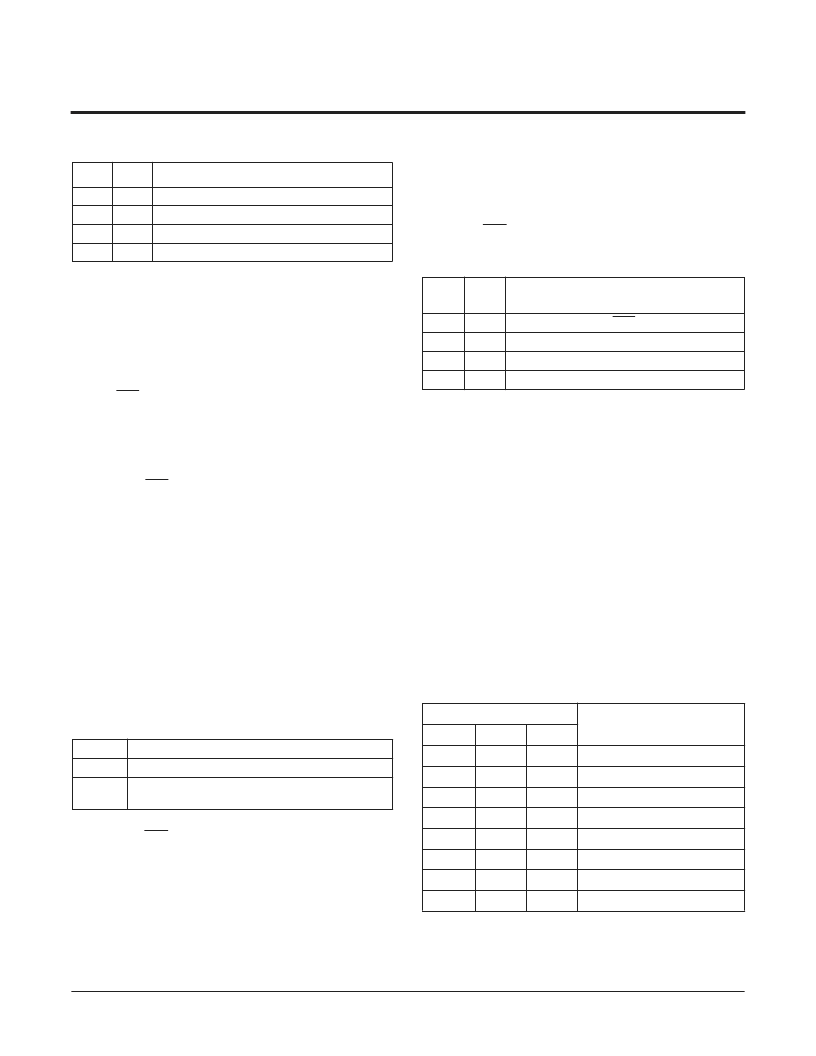

Table 4. Watchdog Timer Time-Out Options

INTERRUPT CONTROL AND FREQUENCY

OUTPUT REGISTER (INT)

Interrupt Control and Status Bits (IM, AL1E, AL0E)

There are two Interrupt Control bits, Alarm 1 Interrupt

Enable (AL1E) and Alarm 0 Interrupt Enable (AL0E) to

specifically enable or disable the alarm interrupt signal

output (IRQ). The interrupts are enabled when either the

AL1E and AL0E bits are set to ‘1’, respectively.

Two volatile bits (AL1 and AL0), associated with the two

alarms respectively, indicate if an alarm has happened.

These bits are set on an alarm condition regardless of

whether the IRQ interrupt is enabled. The AL1 and AL0

bits in the status register are reset by the falling edge of

the eighth clock of a read of the register containing the

bits.

Pulse Interrupt Mode

The pulsed interrrupt mode allows for repetitive or

recurring alarm functionality. Hence an repetitive or

recurring alarm can be set for every n

th

second, or n

th

minute, or n

th

hour, or n

th

date, or for the same day of

the week. The pulsed interrupt mode can be consid-

ered a repetitive interrupt mode, with the repetition rate

set by the time setting of the alarm.

The Pulse Interrupt Mode is enabled when the IM bit is

set.

The Alarm IRQ output will output a single pulse of

short duration (approximately 10-40ms) once the

alarm condition is met. If the interrupt mode bit (IM bit)

is set, then this pulse will be periodic.

Programmable Frequency Output Bits—FO1, FO0

These are two output control bits. They select one of

three divisions of the internal oscillator, that is applied

to the PHZ output pin. Table 5 shows the selection bits

for this output. When using the PHZ output function,

the Alarm IRQ output function is disabled.

Table 5. Programmable Frequency Output Bits

ON-CHIP OSCILLATOR COMPENSATION

Digital Trimming Register (DTR) — DTR2, DTR1 and

DTR0 (Non-Volatile)

The digital trimming Bits DTR2, DTR1 and DTR0

adjust the number of counts per second and average

the ppm error to achieve better accuracy.

DTR2 is a sign bit. DTR2=0 means frequency

compensation is > 0. DTR2=1 means frequency

compensation is < 0.

DTR1 and DTR0 are scale bits. DTR1 gives 10 ppm

adjustment and DTR0 gives 20 ppm adjustment.

A range from -30ppm to +30ppm can be represented

by using three bits above.

Table 6. Digital Trimming Registers

WD1 WD0

0

0

1

1

Watchdog Time-Out Period

0

1

0

1

1.75 seconds

750 milliseconds

250 milliseconds

Disabled (default)

IM Bit

0

Interrupt / Alarm Frequency

Single Time Event Set By Alarm

Repetitive / Recurring Time Event Set By

Alarm

1

FO1

0

0

1

1

FO0

0

1

0

1

Output Frequency

(average of 100 samples)

Alarm IRQ output

32.768kHz

4096Hz

1Hz

DTR Register

DTR2

DTR1

0

0

0

0

1

1

1

1

Estimated frequency

PPM

0 (Default)

+10

+20

+30

0

-10

-20

-30

DTR0

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X1228V14IZ-4.5A | 16 Characters x 1 Lines, 5x7 Dot Matrix Character and Cursor |

| X1228V14Z-2.7A | EXT. DISTANCE DATA CABLE 25 CO |

| X1228S14Z-2.7T1 | EXT DIST RS232 DATA CBL DB25 MALE - DB25 FEMALE |

| X1228V14I-2.7A | RTC Module With CPU Supervisor |

| X1228V14I-4.5A | DIODE 05 TVS SO8 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X1228ZY WAF | 制造商:Intersil Corporation 功能描述: |

| X122K | 制造商:IQD Frequency Products 功能描述:CRYSTAL OSCILLATOR 12.288000MHZ |

| X122-SERIES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral IC |

| X123-133.33M | 制造商:CONNOR-WINFIELD 制造商全稱:Connor-Winfield Corporation 功能描述:5.0x7.0mm Surface Mount LVCMOS Clock Oscillator Series |

| X123241-RDS | 制造商:Honeywell Sensing and Control 功能描述:ATOM & PROX |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。