- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371190 > X1243S8 (INTERSIL CORP) Real Time Clock/Calendar/Alarm with EEPROM PDF資料下載

參數(shù)資料

| 型號: | X1243S8 |

| 廠商: | INTERSIL CORP |

| 元件分類: | XO, clock |

| 英文描述: | Real Time Clock/Calendar/Alarm with EEPROM |

| 中文描述: | 1 TIMER(S), REAL TIME CLOCK, PDSO8 |

| 封裝: | PLASTIC, SOIC-8 |

| 文件頁數(shù): | 10/18頁 |

| 文件大小: | 90K |

| 代理商: | X1243S8 |

X1243

10

the address counter would point to location 7 on the

page that was just written. If the master supplies more

than the maximum bytes in a page, then the previously

loaded data is over written by the new data, one byte

at a time.

The master terminates the Data Byte loading by issu-

ing a stop condition, which causes the device to begin

the non-volatile write cycle. As with the byte write

operation, all inputs are disabled until completion of

the internal write cycle. Refer to Figure 8 for the

address, acknowledge, and data transfer sequence.

Stops and Write Modes

Stop conditions that terminate write operations must

be sent by the master after sending at least 1 full data

byte and it’s associated ACK signal. If a stop is issued

in the middle of a data byte, or before 1 full data byte +

ACK is sent, then the device will reset itself without

performing the write. The contents of the array will not

be affected.

Acknowledge Polling

The disabling of the inputs during non-volatile write

cycles can be used to take advantage of the typical

5mS write cycle time. Once the stop condition is

issued to indicate the end of the master’s byte load

operation, the device initiates the internal non-volatile

write cycle. Acknowledge polling can be initiated

immediately. To do this, the master issues a start con-

dition followed by the Slave Address Byte for a write or

read operation. If the device is still busy with the non-

volatile write cycle then no ACK will be returned. If the

device has completed the write operation, an ACK will

be returned and the host can then proceed with the read

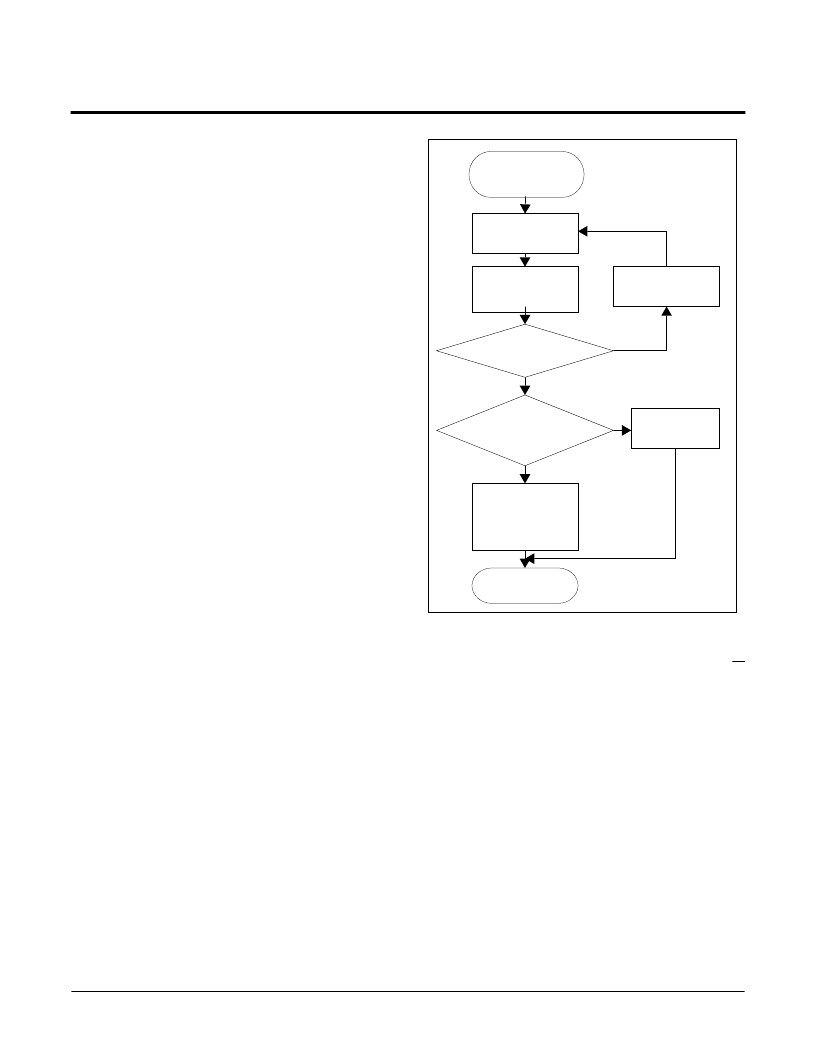

or write operation. Refer to the flow chart in Table 9.

READ OPERATIONS

There are three basic read operations: Current

Address Read, Random Read, and Sequential Read.

Current Address Read

Internally the device contains an address counter that

maintains the address of the last word read incre-

mented by one. Therefore, if the last read was to

address n, the next read operation would access data

from address n+1. On power up, the sixteen bit

address is initialized to 0h. In this way, a current

address read can be initiated immediately after the

power on reset to download the contents of memory

starting at the first location.

Figure 9. Acknowledge Polling Sequence

Upon receipt of the Slave Address Byte with the R/W

bit set to one, the device issues an acknowledge and

then transmits the eight bits of the Data Byte. The

master terminates the read operation when it does not

respond with an acknowledge during the ninth clock

and then issues a stop condition. Refer to Figure 10

for the address, acknowledge, and data transfer

sequence.

It should be noted that the ninth clock cycle of the read

operation is not a “don’t care.” To terminate a read

operation, the master must either issue a stop condi-

tion during the ninth cycle or hold SDA HIGH during

the ninth clock cycle and then issue a stop condition.

ACK

returned

Issue Slave

Address Byte

(Read or Write)

Byte load completed

by issuing STOP.

Enter ACK Polling

Issue STOP

Issue START

NO

YES

Issue STOP

NO

Continue normal

Read or Write

command

sequence

PROCEED

YES

nonvolatile write

Cycle complete.

Continue command

sequence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X1243S8I | Real Time Clock/Calendar/Alarm with EEPROM |

| X1243V8 | Real Time Clock/Calendar/Alarm with EEPROM |

| X125-55FA | 30V Single N-Channel HEXFET Power MOSFET in a TO-220AB package; Similar to the IRF3703 with Lead-Free Packaging. |

| X125-56FA | 30V Single N-Channel HEXFET Power MOSFET in a TO-262 package; Similar to IRF3708L with Lead Free Packaging |

| X125-57FA | BEACON STATIC 12VDC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X1243S8I | 制造商:Intersil Corporation 功能描述: 制造商:XICOR 功能描述: |

| X1243V8 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Real Time Clock/Calendar/Alarm with EEPROM |

| X-1244 | 制造商:Pulse 功能描述:TRANSFORMERS - Rail/Tube |

| X124K | 制造商:IQD Frequency Products 功能描述:CRYSTAL OSCILLATOR 8.192000MHZ |

| X124LE0 | 制造商:SENSORTECHNICS 制造商全稱:Sensortechnics GmbH 功能描述:8 mm switching soleniod valves |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。