- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371311 > XC2S600E-7FG676C FPGA PDF資料下載

參數(shù)資料

| 型號: | XC2S600E-7FG676C |

| 英文描述: | FPGA |

| 中文描述: | FPGA的 |

| 文件頁數(shù): | 12/21頁 |

| 文件大?。?/td> | 183K |

| 代理商: | XC2S600E-7FG676C |

Spartan-IIE 1.8V FPGA Family: DC and Switching Characteristics

12

www.xilinx.com

1-800-255-7778

DS077-3 (v2.0) November 18, 2002

Product Specification

R

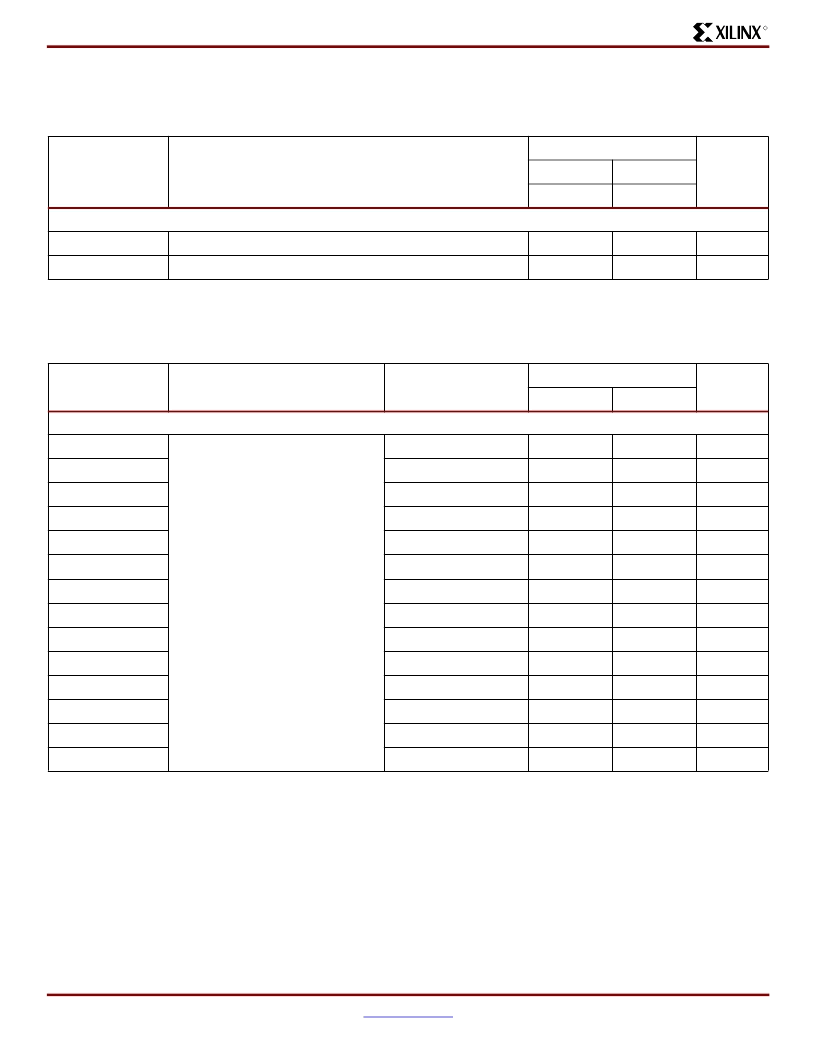

Clock Distribution Switching Characteristics

T

GPIO

is specified for LVTTL levels. For other standards, adjust T

GPIO

with the values shown in

I/O Standard Global Clock

Input Adjustments

.

I/O Standard Global Clock Input Adjustments

Delays associated with a global clock input pad are specified for LVTTL levels. For other standards, adjust the delays by the

values shown. A delay adjusted in this way constitutes a worst-case limit.

Symbol

Description

Speed Grade

Units

-7

-6

Max

Max

GCLK IOB and Buffer

T

GPIO

T

GIO

Global clock pad to output

0.7

0.7

ns

Global clock buffer I input to O output

0.45

0.5

ns

Symbol

Description

Standard

Speed Grade

Units

-7

-6

Data Input Delay Adjustments

T

GPLVTTL

T

GPLVCMOS2

T

GPLVCMOS18

T

GPLVCDS

T

GPLVPECL

T

GPPCI33_3

T

GPPCI66_3

T

GPGTL

T

GPGTLP

T

GPHSTL

T

GPSSTL2

T

GPSSTL3

T

GPCTT

T

GPAGP

Standard-specific global clock

input delay adjustments

LVTTL

0

0

ns

LVCMOS2

0

0

ns

LVCMOS18

0.2

0.2

ns

LVDS

0.38

0.38

ns

LVCPECL

0.38

0.38

ns

PCI, 33 MHz, 3.3V

0.08

0.08

ns

PCI, 66 MHz, 3.3V

–

0.11

–

0.11

ns

GTL

0.37

0.37

ns

GTL+

0.37

0.37

ns

HSTL

0.27

0.27

ns

SSTL2

0.27

0.27

ns

SSTL3

0.27

0.27

ns

CTT

0.33

0.33

ns

AGP

0.27

0.27

ns

Notes:

1.

Input timing for GPLVTTL is measured at 1.4V. For other I/O standards, see the table

Delay Measurement Methodology

, page 11

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC3020B | |

| XC2018B | |

| XC3042B | |

| XC3120-5PC68C | Field Programmable Gate Array (FPGA) |

| XC3120-5PC68I | Field Programmable Gate Array (FPGA) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S600E-7FG676I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S600E-7FGG456C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S600E-7FGG456I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S600E-7FGG676C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S600E-7FGG676I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。