- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371311 > XC2S600E-7FG676C FPGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC2S600E-7FG676C |

| 英文描述: | FPGA |

| 中文描述: | FPGA的 |

| 文件頁數(shù): | 6/21頁 |

| 文件大小: | 183K |

| 代理商: | XC2S600E-7FG676C |

Spartan-IIE 1.8V FPGA Family: DC and Switching Characteristics

6

www.xilinx.com

1-800-255-7778

DS077-3 (v2.0) November 18, 2002

Product Specification

R

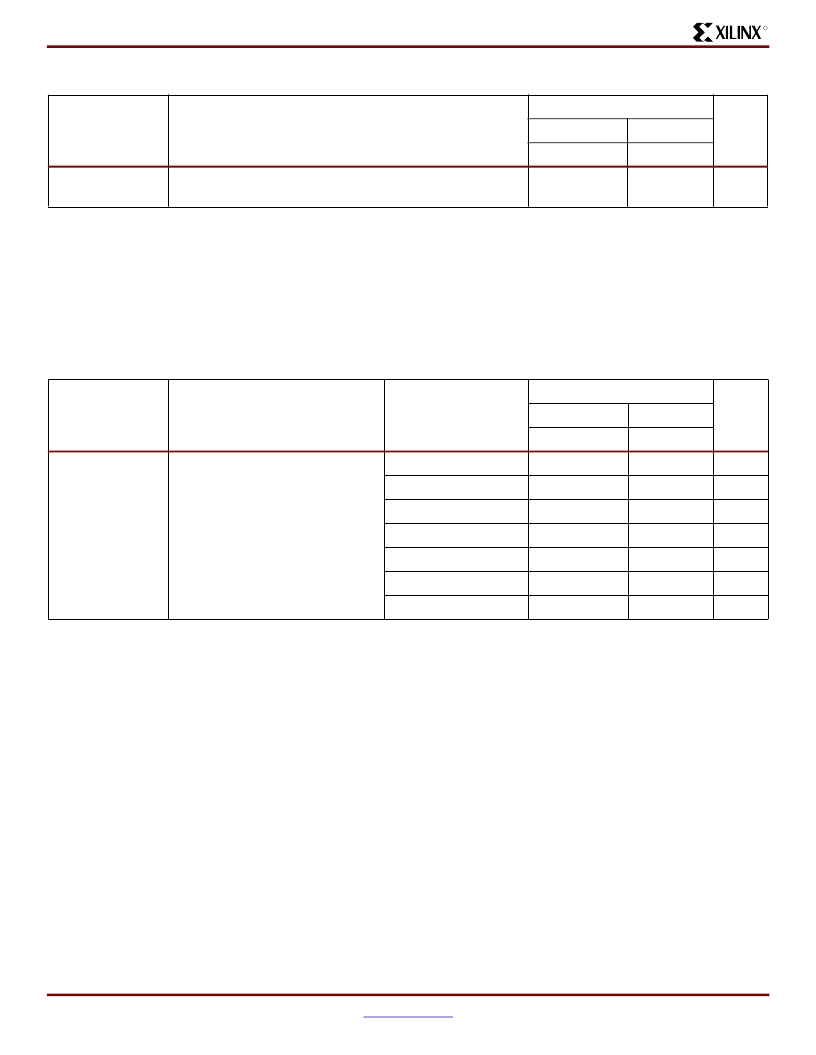

Global Clock Setup and Hold for LVTTL Standard,

with

DLL (Pin-to-Pin)

Global Clock Setup and Hold for LVTTL Standard,

without

DLL (Pin-to-Pin)

Symbol

Description

Speed Grade

Units

-7

-6

Min

Min

T

PSDLL

/ T

PHDLL

Input setup and hold time relative to global clock input signal

for LVTTL standard, no delay, IFF,

(1)

with

DLL

1.6 / 0

1.7 / 0

ns

Notes:

1.

2.

IFF = Input Flip-Flop or Latch

Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured

relative to the Global Clock input signal with the slowest route and heaviest load.

DLL output jitter is already included in the timing calculation.

For data input with different standards, adjust the setup time delay by the values shown in

IOB Input Delay Adjustments for

Different Standards

, page 8

. For a global clock input with standards other than LVTTL, adjust delays with values from the

I/O

Standard Global Clock Input Adjustments

, page 12

.

A zero hold time listing indicates no hold time or a negative hold time.

3.

4.

5.

Symbol

Description

Device

Speed Grade

Units

-7

-6

Min

Min

T

PSFD

/ T

PHFD

Input setup and hold time relative

to global clock input signal for

LVTTL standard, no delay, IFF,

(1)

without

DLL

XC2S50E

1.8 / 0

1.8 / 0

ns

XC2S100E

1.8 / 0

1.8 / 0

ns

XC2S150E

1.9 / 0

1.9 / 0

ns

XC2S200E

1.9 / 0

1.9 / 0

ns

XC2S300E

2.0 / 0

2.0 / 0

ns

XC2S400E

2.0 / 0

2.0 / 0

ns

XC2S600E

2.1 / 0

2.1 / 0

ns

Notes:

1.

2.

IFF = Input Flip-Flop or Latch

Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured

relative to the Global Clock input signal with the slowest route and heaviest load.

For data input with different standards, adjust the setup time delay by the values shown in

IOB Input Delay Adjustments for

Different Standards

, page 8

. For a global clock input with standards other than LVTTL, adjust delays with values from the

I/O

Standard Global Clock Input Adjustments

, page 12

.

3.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC3020B | |

| XC2018B | |

| XC3042B | |

| XC3120-5PC68C | Field Programmable Gate Array (FPGA) |

| XC3120-5PC68I | Field Programmable Gate Array (FPGA) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S600E-7FG676I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S600E-7FGG456C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S600E-7FGG456I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S600E-7FGG676C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S600E-7FGG676I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。