- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄300161 > XCV405E-6FG676I (XILINX INC) Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays PDF資料下載

參數(shù)資料

| 型號: | XCV405E-6FG676I |

| 廠商: | XILINX INC |

| 元件分類: | FPGA |

| 英文描述: | Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| 中文描述: | FPGA, 2400 CLBS, 129600 GATES, 357 MHz, PBGA676 |

| 封裝: | PLASTIC, FBGA-676 |

| 文件頁數(shù): | 16/20頁 |

| 文件大小: | 191K |

| 代理商: | XCV405E-6FG676I |

Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays

DS025-3 (v2.3.2) March 14, 2003

Module 3 of 4

1-800-255-7778

5

R

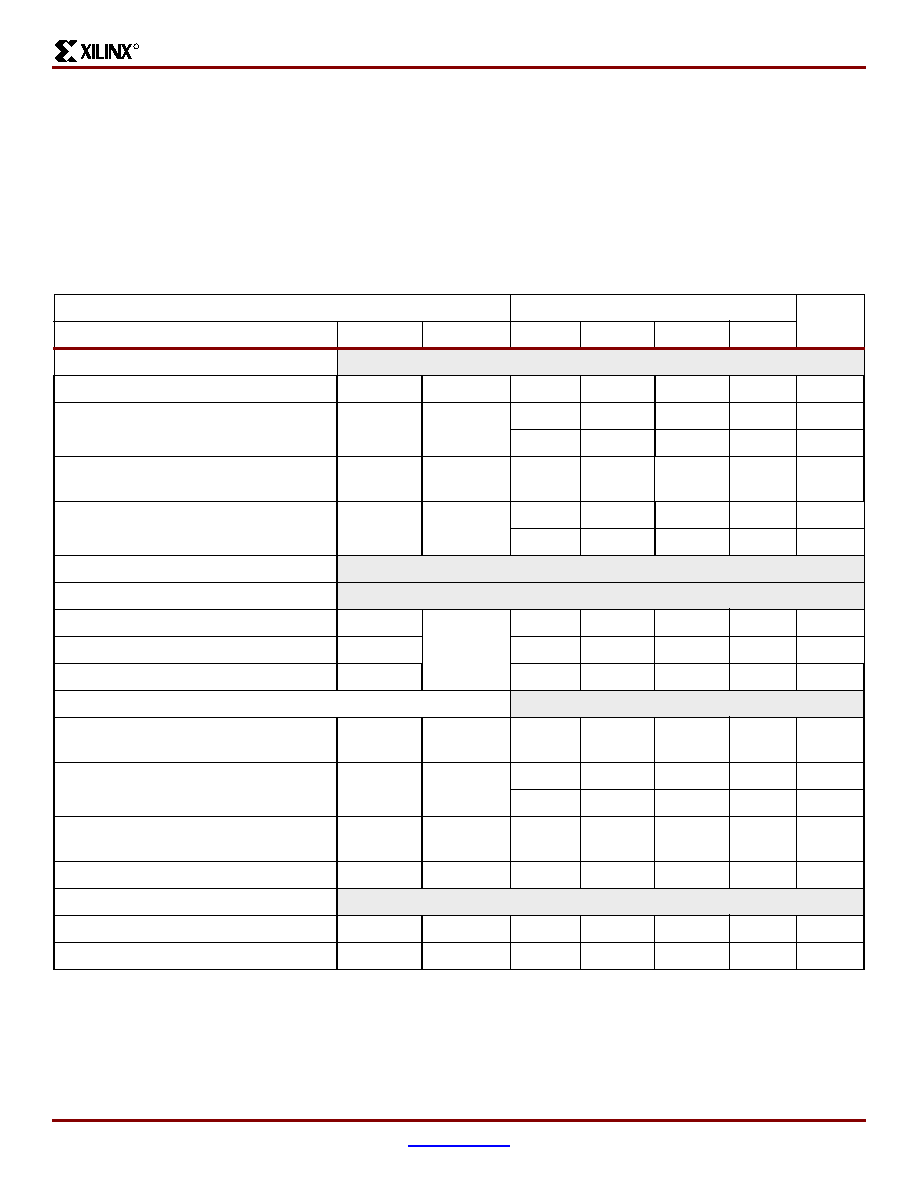

Virtex-E Switching Characteristics

All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed

below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported

by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation net list. All

timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all

Virtex-E devices unless otherwise noted.

IOB Input Switching Characteristics

Input delays associated with the pad are specified for LVTTL levels. For other standards, adjust the delays with the values

Speed Grade(2)

Units

Description(1)

Symbol

Device

Min

-8

-7

-6

Propagation Delays

Pad to I output, no delay

TIOPI

All

0.43

0.8

ns, max

Pad to I output, with delay

TIOPID

XCV405E

0.51

1.0

ns, max

XCV812E

0.55

1.1

ns, max

Pad to output IQ via transparent latch,

no delay

TIOPLI

All

0.75

1.4

1.5

1.6

ns, max

Pad to output IQ via transparent latch,

with delay

TIOPLID

XCV405E

1.55

3.5

3.6

3.7

ns, max

XCV812E

1.55

3.5

3.6

3.7

ns, max

Propagation Delays

Clock

Minimum Pulse Width, High

TCH

All

0.56

1.2

1.3

1.4

ns, min

Minimum Pulse Width, Low

TCL

0.56

1.2

1.3

1.4

ns, min

Clock CLK to output IQ

TIOCKIQ

0.18

0.4

0.7

ns, max

Setup and Hold Times with respect to Clock at IOB Input Register

Pad, no delay

TIOPICK /

TIOICKP

All

0.69 / 0

1.3 / 0

1.4 / 0

1.5 / 0

ns, min

Pad, with delay

TIOPICKD /

TIOICKPD

XCV405E

1.49 / 0

3.4 / 0

3.5 / 0

ns, min

XCV812E

1.49 / 0

3.4 / 0

3.5 / 0

ns, min

ICE input

TIOICECK /

TIOCKICE

All

0.28 /

0.0

0.55 /

0.01

0.7 /

0.01

0.7 /

0.01

ns, min

SR input (IFF, synchronous)

TIOSRCKI

All

0.38

0.8

0.9

1.0

ns, min

Set/Reset Delays

SR input to IQ (asynchronous)

TIOSRIQ

All

0.54

1.1

1.2

1.4

ns, max

GSR to output IQ

TGSRQ

All

3.88

7.6

8.5

9.7

ns, max

Notes:

1.

A Zero “0” Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed “best-case”, but

if a “0” is listed, there is no positive hold time.

2.

Input timing i for LVTTL is measured at 1.4 V. For other I/O standards, see Table 3.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XDMR06A-1 | 7 SEG NUMERIC DISPLAY, RED, 8 mm |

| XH-H | FEMALE, TWO PART BOARD CONNECTOR |

| XHFR-08V-S | 8 CONTACT(S), FEMALE, TWO PART BOARD CONNECTOR |

| XK-1-FREQ-CL | QUARTZ CRYSTAL RESONATOR, 3.2 MHz - 36 MHz |

| XK-1T-FREQ-CL | QUARTZ CRYSTAL RESONATOR, 3.2 MHz - 36 MHz |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCV405E-6FG900C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-6FG900I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-7BG404C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-7BG404I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV405E-7BG556C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。