- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16433 > XR16V798IQ-0A-EVB (Exar Corporation)EVAL BOARD FOR XR16V798-A 100QFP PDF資料下載

參數(shù)資料

| 型號(hào): | XR16V798IQ-0A-EVB |

| 廠商: | Exar Corporation |

| 文件頁(yè)數(shù): | 8/56頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | EVAL BOARD FOR XR16V798-A 100QFP |

| 設(shè)計(jì)資源: | XR17V798/794 Eval Board Schematic |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)

XR16V798

16

HIGH PERFORMANCE 2.25V TO 3.6V OCTAL UART WITH FRACTIONAL BAUD RATE

REV. 1.0.1

2.11

Auto Xon/Xoff (Software) Flow Control

When software flow control is enabled (See Table 18), the 798 compares one or two sequential receive data

characters with the programmed Xon-1,2 or Xoff-1,2 character value(s). If receive character(s) (RX) match the

programmed Xoff-1,2 value(s), the 798 will halt transmission (TX) as soon as the current character has

completed transmission. When a match occurs, the Xoff (if enabled via IER bit-5) flag will be set and the

interrupt output pin will be activated. Following a suspension due to a match of the Xoff character(s), the 798

will monitor the receive data stream for a match to the Xon-1,2 character(s). If a match is found, the 798 will

resume operation and clear the flags (ISR bit-4).

Reset initially sets the contents of the Xon1, Xon2, Xoff1 and Xoff2 flow control registers to ’0’. Following reset,

any desired Xon/Xoff value can be used for software flow control. Different conditions can be set to detect Xon/

Xoff characters (See Table 18) and suspend/resume transmissions. When double 8-bit Xon/Xoff characters

are selected, the 798 compares two consecutive receive characters with two software flow control 8-bit values

(Xon1, Xon2, Xoff1, Xoff2) and controls TX transmissions accordingly. Under the above described flow control

mechanisms, flow control characters are not placed (stacked) in the user accessible RX data buffer or FIFO.

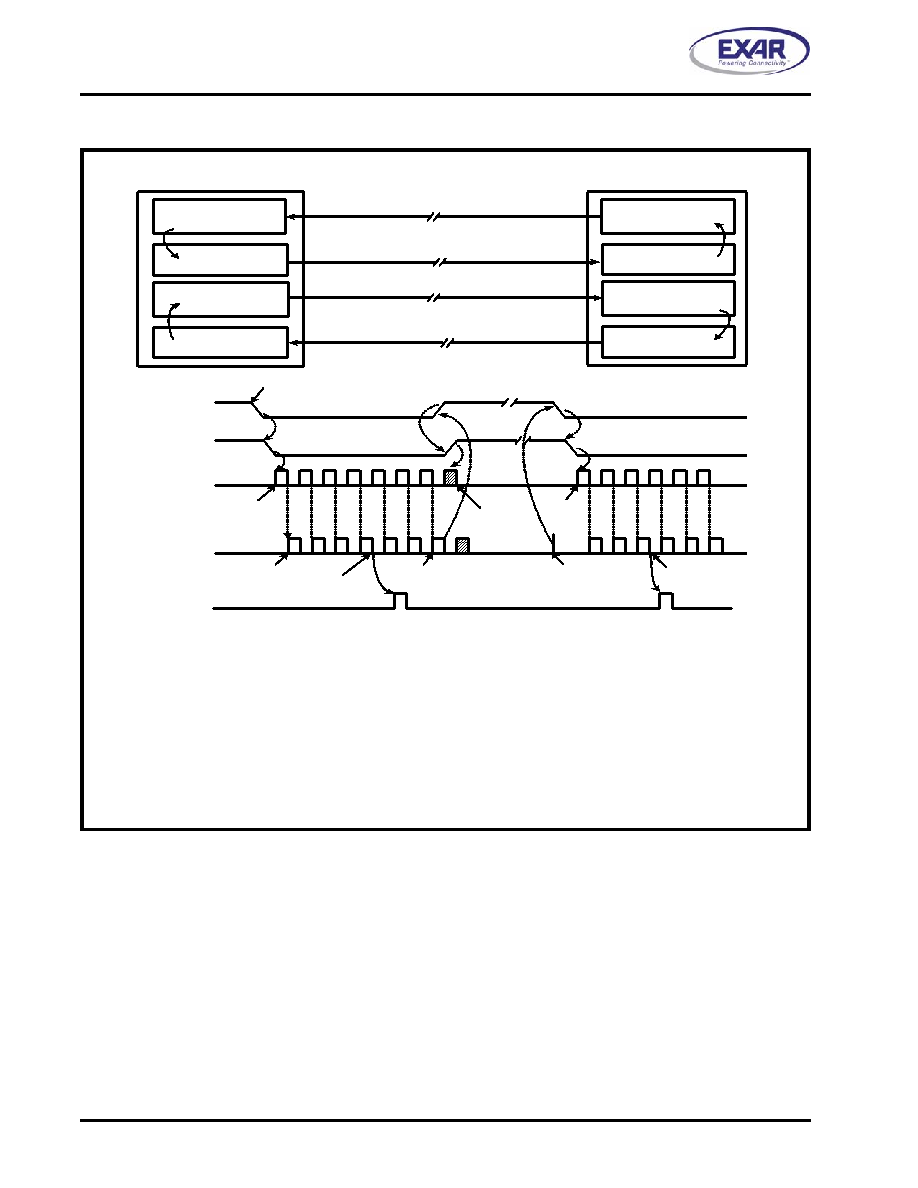

FIGURE 9. AUTO RTS/DTR AND CTS/DSR FLOW CONTROL OPERATION

The local UART (UARTA) starts data transfer by asserting RTSA# (1). RTSA# is normally connected to CTSB# (2) of

remote UART (UARTB). CTSB# allows its transmitter to send data (3). TXB data arrives and fills UARTA receive FIFO

(4). When RXA data fills up to its receive FIFO trigger level, UARTA activates its RXA data ready interrupt (5) and con-

tinues to receive and put data into its FIFO. If interrupt service latency is long and data is not being unloaded, UARTA

monitors its receive data fill level to match the upper threshold of RTS delay and de-assert RTSA# (6). CTSB# follows

(7) and request UARTB transmitter to suspend data transfer. UARTB stops or finishes sending the data bits in its trans-

mit shift register (8). When receive FIFO data in UARTA is unloaded to match the lower threshold of RTS delay (9),

UARTA re-asserts RTSA# (10), CTSB# recognizes the change (11) and restarts its transmitter and data flow again until

next receive FIFO trigger (12). This same event applies to the reverse direction when UARTA sends data to UARTB

with RTSB# and CTSA# controlling the data flow.

RTSA#

CTSB#

RXA

TXB

Transmitter

Receiver FIFO

Trigger Reached

Auto RTS

Trigger Level

Auto CTS

Monitor

RTSA#

TXB

RXA FIFO

CTSB#

Remote UART

UARTB

Local UART

UARTA

ON

OFF

ON

Suspend

Restart

RTS High

Threshold

Data Starts

ON

OFF

ON

Assert RTS# to Begin

Transmission

1

2

3

4

5

6

7

Receive

Data

RTS Low

Threshold

9

10

11

Receiver FIFO

Trigger Reached

Auto RTS

Trigger Level

Transmitter

Auto CTS

Monitor

RTSB#

CTSA#

RXB

TXA

INTA

(RXA FIFO

Interrupt)

RX FIFO

Trigger Level

RX FIFO

Trigger Level

8

12

RTSCTS1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XR16V698IQ-0B-EVB | EVAL BOARD FOR XR16V698-B 100QFP |

| XR16V698IQ-0A-EVB | EVAL BOARD FOR XR16V698-A 100QFP |

| KIT33972AEWEVBE | KIT EVALUATION FOR MC33972 |

| EBM31DCMS | CONN EDGECARD 62POS .156 WW |

| VI-J1L-EX | CONVERTER MOD DC/DC 28V 75W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR16V798IQ-0B-EVB | 功能描述:UART 接口集成電路 Supports V798 100 ld QFP,PCI Interface RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16V798IQ-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16V798IQTR-F | 制造商:Exar Corporation 功能描述:UART 8-CH 64Byte FIFO 2.5V/3.3V 100-Pin PQFP T/R |

| XR-1790 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Audio Schematic |

| XR17C152 | 制造商:EXAR 制造商全稱:EXAR 功能描述:5V PCI BUS DUAL UART |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。