- 您現在的位置:買賣IC網 > PDF目錄376455 > XR17D158CV (EXAR CORP) UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART PDF資料下載

參數資料

| 型號: | XR17D158CV |

| 廠商: | EXAR CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART |

| 中文描述: | 8 CHANNEL(S), 6.25M bps, SERIAL COMM CONTROLLER, PQFP144 |

| 封裝: | 20 X 20 MM, 1.40 MM HEIGHT, TQFP-144 |

| 文件頁數: | 6/72頁 |

| 文件大?。?/td> | 1520K |

| 代理商: | XR17D158CV |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁

XR17D158

UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART

xr

REV. 1.2.1

6

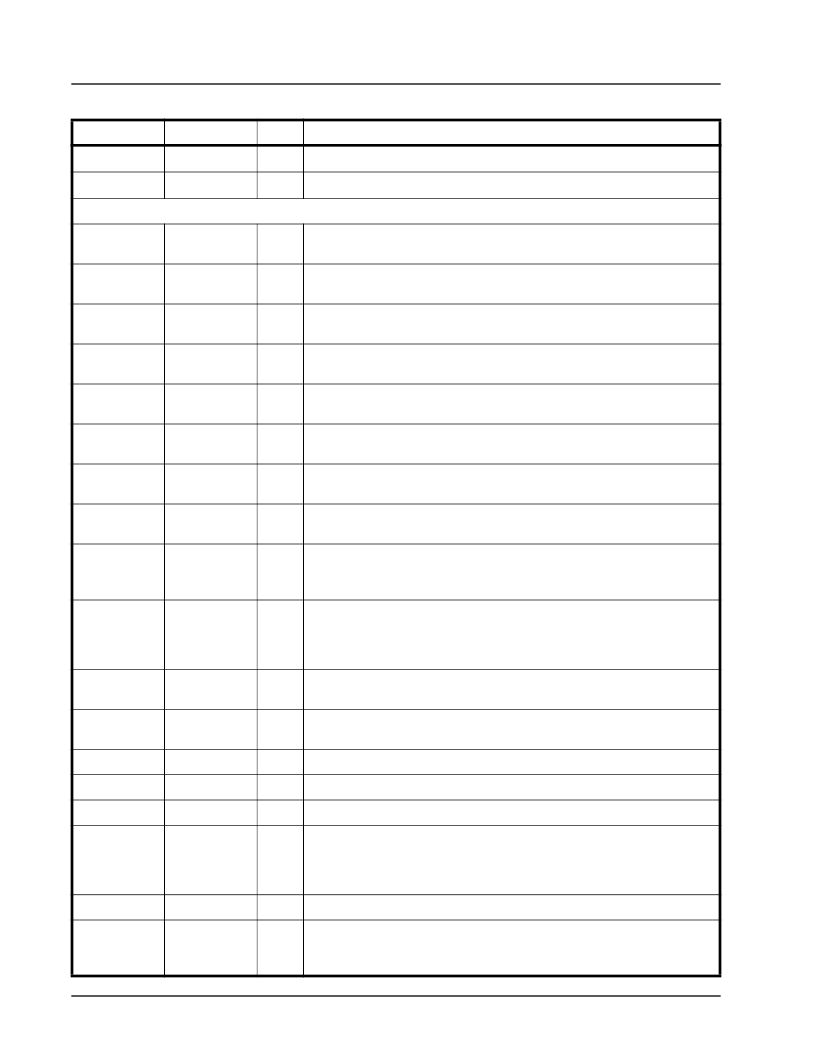

CD7#

50

I

UART channel 7

Carrier Detect or general purpose input (active low).

RI7#

51

I

UART channel 7 Ring Indicator or general purpose

input (active low).

ANCILLARY SIGNALS

MPIO0

108

I/O

Multi-purpose input/output 0. The function of this pin is defined thru the Con-

figuration Register MPIOSEL, MPIOLVL, MPIOINV, MPIO3T and MPIOINT

MPIO1

107

I/O

Multi-purpose input/output 1. The function of this pin is defined thru the Con-

figuration Register MPIOSEL, MPIOLVL, MPIOINV, MPIO3T and MPIOINT.

MPIO2

74

I/O

Multi-purpose input/output 2. The function of this pin is defined thru the Con-

figuration Register MPIOSEL, MPIOLVL, MPIOINV, MPIO3T and MPIOINT.

MPIO3

73

I/O

Multi-purpose input/output 3. The function of this pin is defined thru the Con-

figuration Register MPIOSEL, MPIOLVL, MPIOINV, MPIO3T and MPIOINT.

MPIO4

68

I/O

Multi-purpose input/output 4. The function of this pin is defined thru the Con-

figuration Register MPIOSEL, MPIOLVL, MPIOINV, MPIO3T and MPIOINT.

MPIO5

67

I/O

Multi-purpose input/output 5. The function of this pin is defined thru the Con-

figuration Register MPIOSEL, MPIOLVL, MPIOINV, MPIO3T and MPIOINT.

MPIO6

66

I/O

Multi-purpose input/output 6. The function of this pin is defined thru the Con-

figuration Register MPIOSEL, MPIOLVL, MPIOINV, MPIO3T and MPIOINT.

MPIO7

65

I/O

Multi-purpose input/output 7. The function of this pin is defined thru the Con-

figuration Register MPIOSEL, MPIOLVL, MPIOINV, MPIO3T and MPIOINT.

EECK

116

O

Serial clock to EEPROM.

An internal clock of CLK divide by 256 is used for

reading the vendor and sub-vendor ID during power up or reset. However, it

can be manually clocked thru the Configuration Register REGB.

EECS

115

O

Chip select to a EEPROM device like 93C46. It is manually selectable thru

the Configuration Register REGB. Requires a pull-up 4.7K ohm resistor for

external sensing of EEPROM during power up. See DAN112 for further

details.

EEDI

114

O

Write data to EEPROM device. It is manually accessible thru the Configura-

tion Register REGB.

EEDO

113

I

Read data from EEPROM device. It is manually accessible thru the Configu-

ration Register REGB.

XTAL1

110

I

Crystal or external clock input.

XTAL2

109

O

Crystal or buffered clock output.

TMRCK

69

I

16-bit timer/counter external clock input.

ENIR

70

I

Infrared mode enable (active high). This pin is sampled during power up, fol-

lowing a hardware reset (RST#) or soft-reset (register RESET). It can be

used to start up all 8 UARTs in the infrared mode. The sampled logic state is

transferred to MCR bit-6 in the UART.

TEST#

111

I

Factory Test. Connect to VCC for normal operation.

VCC

64, 90,112

Power supply for the UART core logic - 5V ONLY. This power supply deter-

mines the VOH level of the non-PCI bus interface outputs. See Table 1

for

valid combinations of VCC and VIO that can be used for the XR17D158.

PIN DESCRIPTIONS

N

AME

P

IN

#

T

YPE

D

ESCRIPTION

相關PDF資料 |

PDF描述 |

|---|---|

| XR17L152IM | CAP .068UF 400V PEN FILM 2825 5% |

| XR17L152 | 3.3V PCI BUS DUAL UART |

| XR17L152CM | 3.3V PCI BUS DUAL UART |

| XR2001 | High-Voltage, High-Current Darlington Transistor Arrays |

| XR2002CN | High-Voltage, High-Current Darlington Transistor Arrays |

相關代理商/技術參數 |

參數描述 |

|---|---|

| XR17D158CV-0A-EVB | 功能描述:界面開發(fā)工具 Supports D158 144 ld TQFP, PCI Interface RoHS:否 制造商:Bourns 產品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XR17D158CV-F | 功能描述:UART 接口集成電路 3.3V-5V 64B FIFO temp 0C to 70C; UART RoHS:否 制造商:Texas Instruments 通道數量:2 數據速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17D158CV-F-SIWI | 制造商:Exar Corporation 功能描述:FOR WILLIAMS GAMING THEIR CM'S 制造商:EXAR 功能描述:XR17D158CV-F-SIWI 制造商:EXAR 功能描述:FOR WILLIAMS GAMING THEIR CM'S |

| XR17D158CVTR-F | 制造商:Exar Corporation 功能描述:UART 8-CH 64Byte FIFO 5V 144-Pin LQFP T/R 制造商:Exar Corporation 功能描述:XR17D158CVTR-F |

| XR17D158IV | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數量:2 數據速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。