- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄376455 > XR17L152CM (EXAR CORP) 3.3V PCI BUS DUAL UART PDF資料下載

參數(shù)資料

| 型號(hào): | XR17L152CM |

| 廠(chǎng)商: | EXAR CORP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 3.3V PCI BUS DUAL UART |

| 中文描述: | 2 CHANNEL(S), 3.125M bps, SERIAL COMM CONTROLLER, PQFP100 |

| 封裝: | 14 X 14 MM, 1 MM HEIGHT, TQFP-100 |

| 文件頁(yè)數(shù): | 33/55頁(yè) |

| 文件大小: | 318K |

| 代理商: | XR17L152CM |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)當(dāng)前第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)

XR17L152

3.3V PCI BUS DUAL UART

REV. 1.1.0

á

DISCONTINUED

33

]

ISR[0]: Interrupt Status

Logic 0 = An interrupt is pending and the ISR contents may be used as a pointer to the appropriate interrupt

service routine.

Logic 1 = No interrupt pending (default condition).

ISR[3:1]: Interrupt Status

These bits indicate the source for a pending interrupt at interrupt priority levels 1, 2, 3 and 4 (See Interrupt

Source

Table 12

).

ISR[5:4]: Interrupt Status

These bits are enabled when EFR bit-4 is set to a logic 1. ISR bit-4 indicates that the receiver detected a data

match of the Xon or Xoff character(s). Note that once set to a logic 1, the ISR bit-4 will stay a logic 1 until a Xon

character is received. ISR bit-5 indicates that CTS#/DSR# or RTS#/DTR# has changed state.

ISR[7:6]: FIFO Enable Status

These bits are set to a logic 0 when the FIFOs are disabled. They are set to a logic 1 when the FIFOs are

enabled.

FIFO Control Register (FCR)

This register is used to enable the FIFOs, clear the FIFOs, set the transmit/receive FIFO trigger levels, and

select the DMA mode. The DMA, and FIFO modes are defined as follows:

FCR[0]: TX and RX FIFO Enable

Logic 0 = Disable the transmit and receive FIFO (default).

Logic 1 = Enable the transmit and receive FIFOs. This bit must be set to logic 1 when other FCR bits are

written or they will not be programmed.

FCR[1]: RX FIFO Reset

This bit is only active when FCR bit-0 is a logic 1.

Logic 0 = No receive

FIFO

reset (default).

Logic 1 = Reset the receive FIFO pointers and FIFO level counter logic (the receive shift register is not

cleared or altered). This bit will return to a logic 0 after resetting the FIFO.

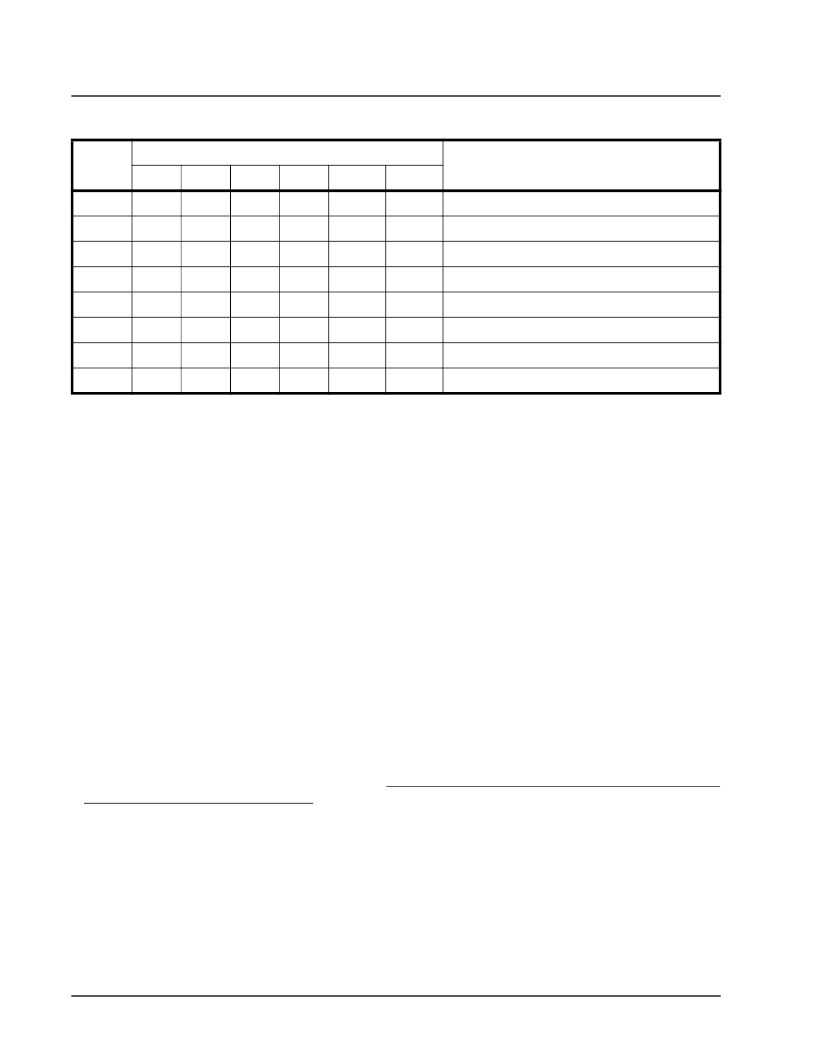

T

ABLE

12: I

NTERRUPT

S

OURCE

AND

P

RIORITY

L

EVEL

P

RIORITY

ISR R

EGISTER

S

TATUS

B

ITS

S

OURCE

OF

THE

INTERRUPT

+

L

EVEL

B

IT

-5

B

IT

-4

B

IT

-3

B

IT

-2

B

IT

-1

B

IT

-0

1

0

0

0

1

1

0

LSR (Receiver Line Status Register)

2

0

0

0

1

0

0

RXRDY (Received Data Ready)

3

0

0

1

1

0

0

RXRDY (Receive Data Time-out)

4

0

0

0

0

1

0

TXRDY (Transmitter Holding Register Empty)

5

0

0

0

0

0

0

MSR (Modem Status Register)

6

0

1

0

0

0

0

RXRDY (Received Xon/Xoff or Special character)

7

1

0

0

0

0

0

CTS#/DSR#, RTS#/DTR# change of state

X

0

0

0

0

0

1

None (default)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XR2001 | High-Voltage, High-Current Darlington Transistor Arrays |

| XR2002CN | High-Voltage, High-Current Darlington Transistor Arrays |

| XR2003 | High-Voltage, High-Current Darlington Transistor Arrays |

| XR2003CN | Programable Driver IC |

| XR2004 | High-Voltage, High-Current Darlington Transistor Arrays |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR17L152IM | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:3.3V PCI BUS DUAL UART |

| XR17L154 | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:3.3V PCI BUS QUAD UART |

| XR17L154CV | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:Telecomm/Datacomm |

| XR17L154IV | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:3.3V PCI BUS QUAD UART |

| XR17V252 | 制造商:EXAR 制造商全稱(chēng):EXAR 功能描述:66 MHZ PCI BUS DUAL UART WITH POWER MANAGEMENT SUPPORT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。