- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16512 > XR19L212IL48-0B-EB (Exar Corporation)EVAL BOARD FOR XR19L202 48QFN PDF資料下載

參數(shù)資料

| 型號: | XR19L212IL48-0B-EB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 20/52頁 |

| 文件大?。?/td> | 0K |

| 描述: | EVAL BOARD FOR XR19L202 48QFN |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

XR19L212

27

REV. 1.0.1

TWO CHANNEL INTEGRATED UART AND RS-232 TRANSCEIVER

4.4.2

Interrupt Clearing:

LSR interrupt is cleared by a read to the LSR register.

RXRDY interrupt is cleared by reading data until FIFO falls below the trigger level.

RXRDY Time-out interrupt is cleared by reading RHR.

TXRDY interrupt is cleared by a read to the ISR register or writing to THR.

MSR interrupt is cleared by a read to the MSR register.

Xoff interrupt is cleared by a read to ISR or when Xon character(s) is received.

Special character interrupt is cleared by a read to ISR or after the next character is received.

RTS# and CTS# flow control interrupts are cleared by a read to the MSR register.

Wake-up Indicator is cleared by a read to the ISR register.

]

ISR[0]: Interrupt Status

Logic 0 = An interrupt is pending and the ISR contents may be used as a pointer to the appropriate interrupt

service routine.

Logic 1 = No interrupt pending (default condition) or the device has come out of sleep mode.

ISR[3:1]: Interrupt Status

These bits indicate the source for a pending interrupt at interrupt priority levels (See Interrupt Source Table 9).

ISR[4]: Xoff or Special Character Interrupt Status (requires EFR bit-4=1)

This bit is enabled when IER[5] = 1. ISR bit-4 indicates that the receiver detected a data match of the Xoff

character(s) or special character (XOFF2).

ISR[5]: RTS#/CTS# Interrupt Status (requires EFR bit-4=1)

This bit is enabled when IER[7] = 1 or IER[6] = 1. ISR bit-5 indicates that the CTS# or RTS# has been de-

asserted.

ISR[7:6]: FIFO Enable Status

These bits are set to a logic 0 when the FIFOs are disabled. They are set to a logic 1 when the FIFOs are

enabled.

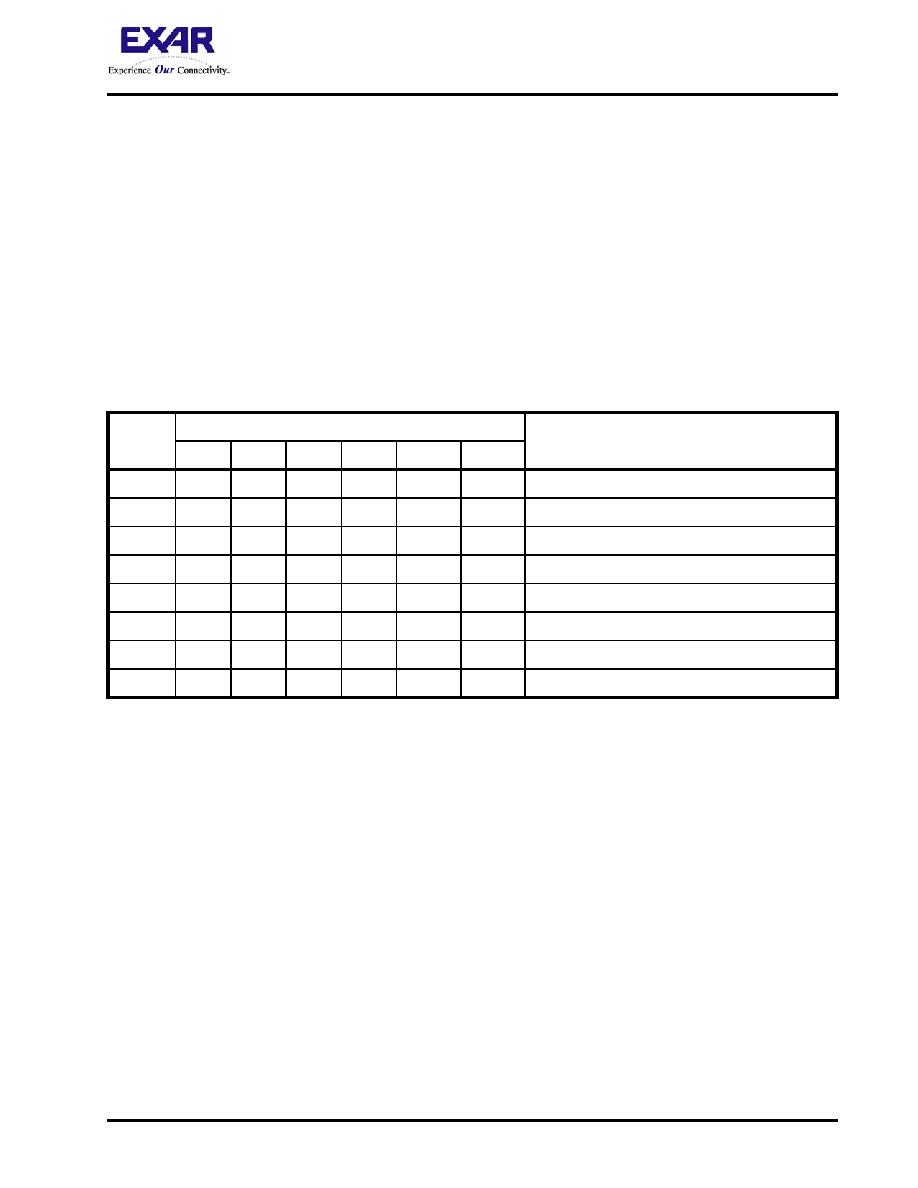

TABLE 9: INTERRUPT SOURCE AND PRIORITY LEVEL

PRIORITY

ISR REGISTER STATUS BITS

SOURCE OF INTERRUPT

LEVEL

BIT-5

BIT-4

BIT-3

BIT-2

BIT-1

BIT-0

1

0

1

0

LSR (Receiver Line Status Register)

2

0

1

0

RXRDY (Receive Data Time-out)

3

0

1

0

RXRDY (Received Data Ready)

4

0

1

0

TXRDY (Transmit Ready)

5

0

MSR (Modem Status Register)

6

0

1

0

RXRDY (Received Xoff or Special character)

7

1

0

CTS#, RTS# change of state

-

0

1

None (default) or Wake-up Indicator

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VI-25M-EX | CONVERTER MOD DC/DC 10V 75W |

| A3BKB-1018G | IDC CABLE- ASR10B/AE10G/APK10B |

| VI-JVT-EZ-S | CONVERTER MOD DC/DC 6.5V 25W |

| UPJ1K470MPD6TD | CAP ALUM 47UF 80V 20% RADIAL |

| H3WWH-2406G | IDC CABLE - HPL24H/AE24G/HPL24H |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR19L212IL48-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR19L212IL48TR-F | 制造商:Exar Corporation 功能描述:UART 2-CH 64Byte FIFO 5V 48-Pin QFN EP T/R 制造商:Exar Corporation 功能描述:XR19L212IL48TR-F |

| XR19L220 | 制造商:EXAR 制造商全稱:EXAR 功能描述:SINGLE CHANNEL INTEGRATED UART AND RS-232 TRANSCEIVER |

| XR19L220_07 | 制造商:EXAR 制造商全稱:EXAR 功能描述:SINGLE CHANNEL INTEGRATED UART AND RS-232 TRANSCEIVER |

| XR19L220IL40 | 制造商:EXAR 制造商全稱:EXAR 功能描述:SINGLE CHANNEL INTEGRATED UART AND RS-232 TRANSCEIVER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。