- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376461 > XRT73LC00A (Exar Corporation) E3/DS3/STS-1 LINE INTERFACE UNIT PDF資料下載

參數(shù)資料

| 型號: | XRT73LC00A |

| 廠商: | Exar Corporation |

| 英文描述: | E3/DS3/STS-1 LINE INTERFACE UNIT |

| 中文描述: | E3/DS3/STS-1線路接口單元 |

| 文件頁數(shù): | 26/53頁 |

| 文件大小: | 376K |

| 代理商: | XRT73LC00A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

XRT73LC00A

E3/DS3/STS-1 LINE INTERFACE UNIT

REV. P1.0.0

xr

PRELIMINARY

23

The manner that the LIU handles Dual-Rail data is

described below and illustrated in Figure 12. The

XRT73LC00A typically samples the data on the TP-

DATA and TNDATA input pins on the falling edge of

TCLK.

TCLK is typically a clock signal that is of the selected

data rate frequency. For the E3 data rate, TCLK is

34.368 MHz. For the DS3 data rate, TCLK is 44.736

MHz and for the SONET STS-1 rate, TCLK is 51.84

MHz. In general, if the XRT73LC00A samples a “1”

on the TPDATA input pin, the Transmit Section of the

device ultimately generates a positive polarity pulse

via the TTIP and TRING output pins across a 1:1

transformer. If the XRT73LC00A samples a “1” on

the TNDATA input pin, the Transmit Section of the de-

vice ultimately generates a negative polarity pulse via

the TTIP and TRING output pins across a 1:1 trans-

former.

2.1.1

Accepting Single-Rail Data from the Ter-

minal Equipment

Do the following if data is to be transmited from the

Terminal Equipment to the XRT73LC00A in Single-

Rail format (a binary data stream) without having to

convert it into a Dual-Rail format.

A.

Configure the XRT73LC00A to operate in the

HOST Mode or,

B.

access the Microprocessor Serial Interface and

write a “1” into the TXBIN (TRANSMIT BINary)

bit-field in Command Register 1.

After taking these steps, the Transmit Logic Block ac-

cepts Single-Rail data via the TPDATA input pin. The

XRT73LC00A samples this input pin on the falling

edge of the TCLK clock signal and encodes it into the

appropriate bipolar line signal across the TTIP and

TRING output pins.

N

OTES

:

1. In this mode the Transmit Logic Block ignores the

TNDATA input pin.

2. If the Transmit Section of the XRT73LC00A is con-

figured to accept Single-Rail data from the Terminal

Equipment, the B3ZS/HDB3 Encoder must be

enabled.

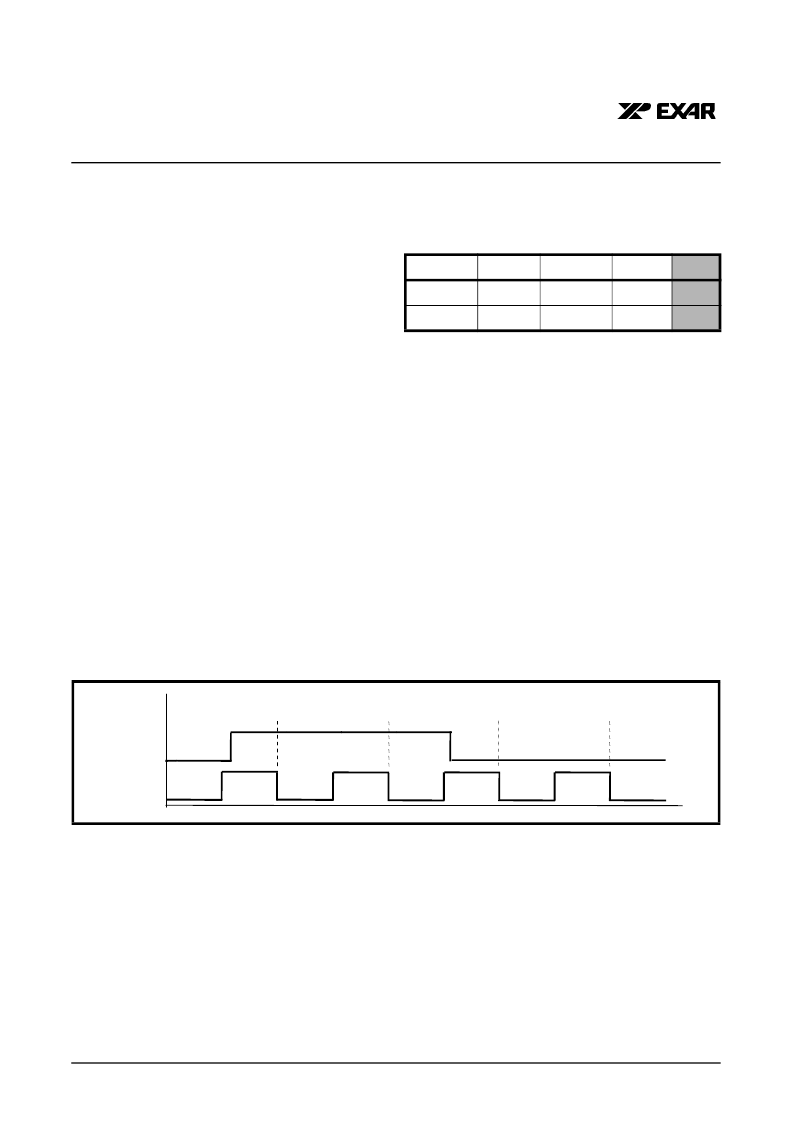

Figure 13 illustrates the behavior of the TPDATA and

TCLK signals when the Transmit Logic Block has

been configured to accept Single-Rail data from the

Terminal Equipment.

2.2

T

HE

T

RANSMIT

C

LOCK

D

UTY

C

YCLE

A

DJUST

C

IR

-

CUITRY

The on-chip Pulse-Shaping circuitry in the Transmit

Section of the XRT73LC00A has the responsibility for

generating pulses of the shape and width to comply

with the applicable pulse template requirement. The

widths of these output pulses are defined by the width

of the half-period pulses in the TCLK signal.

Allowing the widths of the pulses in the TCLK clock

signal to vary significantly could jeopardize the chip’s

ability to generate Transmit Output pulses of the ap-

propriate width, thereby failing the applicable Pulse

Template Requirement Specification. The chips abili-

ty to generate compliant pulses could depend upon

the duty cycle of the clock signal applied to the TCLK

input pin.

In order to combat this phenomenon, the Transmit

Clock Duty Cycle Adjust circuit was designed into the

XRT73LC00A. The Transmit Clock Duty Cycle Adjust

Circuitry is a PLL that was designed to accept clock

pulses via the TCLK input pin at duty cycles ranging

from 30% to 70% and to regenerate these signals

with a 50% duty cycle.

COMMAND REGISTER CR1 (ADDRESS = 0X01)

D4

D3

D2

D1

D0

TXOFF

TAOS

TXCLKINV

TXLEV

TXBIN

X

X

X

X

1

F

IGURE

13. T

HE

B

EHAVIOR

OF

THE

TPDATA

AND

TCLK I

NPUT

S

IGNALS

W

HILE

THE

T

RANSMIT

L

OGIC

B

LOCK

IS

A

CCEPTING

S

INGLE

-R

AIL

D

ATA

F

ROM

THE

T

ERMINAL

E

QUIPMENT

TCLK

TPDATA

Data 1 1 0 0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT73LC00AIV | E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73LC03A | 3 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73LC03AIV | 3 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73LC04A | 4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73LC04AIV | 4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT73LC00A_08 | 制造商:EXAR 制造商全稱:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT73LC00AES | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT73LC00AIV | 功能描述:外圍驅(qū)動器與原件 - PCI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT73LC00AIV-F | 功能描述:外圍驅(qū)動器與原件 - PCI 1-Ch DS3, E3, SONET RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT73LC00AIVTR | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。