- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT75R12 (Exar Corporation) TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR PDF資料下載

參數(shù)資料

| 型號(hào): | XRT75R12 |

| 廠商: | Exar Corporation |

| 英文描述: | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| 中文描述: | 第十二章通道E3/DS3/STS-1線路接口單元與抖動(dòng)衰減器 |

| 文件頁數(shù): | 10/89頁 |

| 文件大?。?/td> | 457K |

| 代理商: | XRT75R12 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

XRT75R12

REV. P1.0.2

PRELIMINARY

TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR

7

F23

AC26

F24

U23

L23

T24

L4

T3

F3

U4

F4

AC1

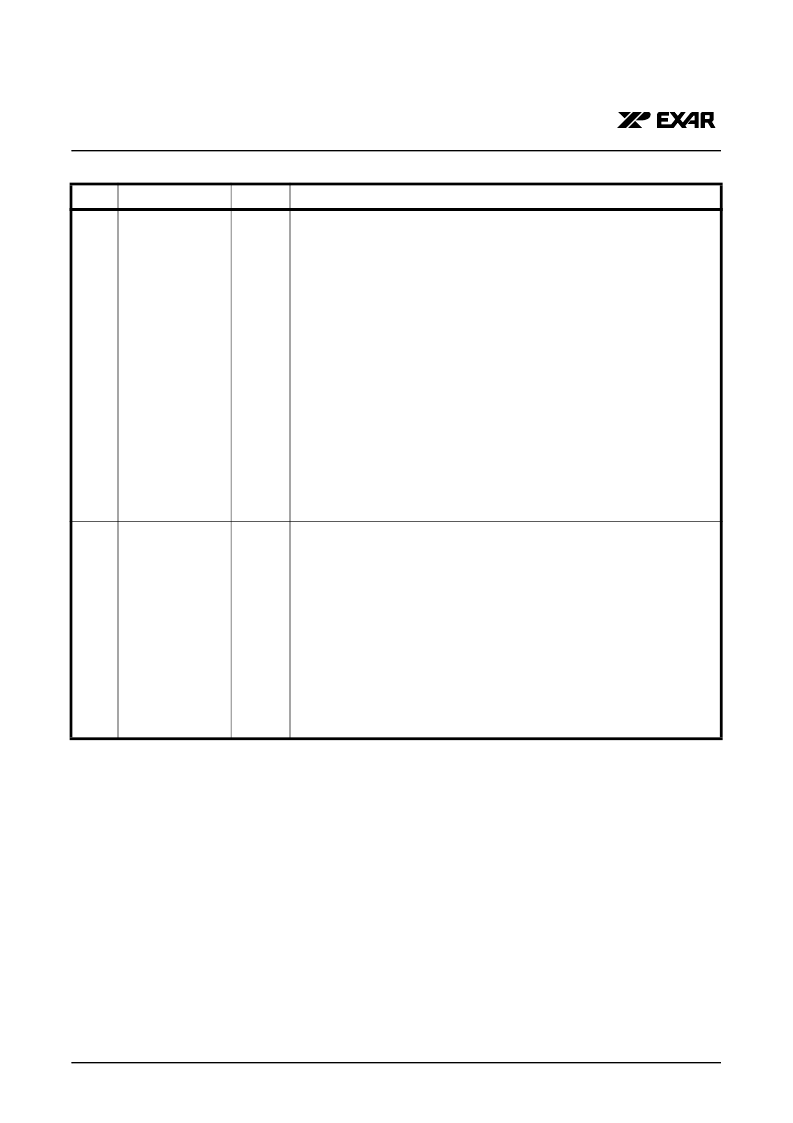

RxNEG/LCV0

RxNEG/LCV1

RxNEG/LCV2

RxNEG/LCV3

RxNEG/LCV4

RxNEG/LCV5

RxNEG/LCV6

RxNEG/LCV7

RxNEG/LCV8

RxNEG/LCV9

RxNEG/LCV10

RxNEG/LCV11

O

Receive Negative Data Output/Line Code Violation

The function of these pins depends on whether the XRT75R12 is configured in

Single Rail or Dual Rail mode.

Dual-Rail Mode - Receive Negative Polarity Data Output

In the Dual-Rail Mode, all negative-polarity data will be output via this pin. The

positive-polarity data will be output via the corresponding RxPOS_n output pin.

In other words, the Receive Section of the corresponding Channel will pulse this

output pin "High" for one period of RxCLK_n anytime it receives a negative-

polarity pulse via the RTIP/RRING input pins.

The data output via this pin is updated upon the active edge of the RCLK_n

output clock signal.

Single-Rail Mode - Line Code Violation Indicator Output

In the Single-Rail Mode, this output pin will function as the Line Code Violation

indicator output.

In this configuration, the Receive Section of the Channel will pulse this output

pin "High" for at least one RCLK period whenever it detects either an LCV (Line

Code Violation) or an EXZ (Excessive Zero Event).

The data that is output via this pin is updated upon the active edge of the

RCLK_n output clock signal.

E24

AC25

J23

V23

K24

T23

K3

T4

J4

V4

E3

AC2

RxCLK0

RxCLK1

RxCLK2

RxCLK3

RxCLK4

RxCLK5

RxCLK6

RxCLK7

RxCLK8

RxCLK9

RxCLK10

RxCLK11

O

Receive Clock Output

This output pin functions as the Receive or recovered clock signal. All Receive

(or recovered) data will output via the RxPOS_n and RxNEG_n outputs upon

the active edge of this clock signal.

Additionally, if the device/channel has been configured to operate in the Single-

Rail Mode, then the RNEG_n/LCV_n output pins will also be updated upon the

active edge of this clock signal.

SYSTEM-SIDE RECEIVE OUTPUT AND RECEIVE CONTROL PINS

P

IN

#

S

IGNAL

N

AME

T

YPE

D

ESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT75R12IB | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75VL00 | E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75VL00IV | E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT79L71 | 1 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

| XRT79L71IB | 1 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT75R12_07 | 制造商:EXAR 制造商全稱:EXAR 功能描述:TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER |

| XRT75R12_0710 | 制造商:EXAR 制造商全稱:EXAR 功能描述:TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER |

| XRT75R12D | 制造商:EXAR 制造商全稱:EXAR 功能描述:TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET |

| XRT75R12D_06 | 制造商:EXAR 制造商全稱:EXAR 功能描述:TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET |

| XRT75R12D_07 | 制造商:EXAR 制造商全稱:EXAR 功能描述:TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。