- 您現在的位置:買賣IC網 > PDF目錄373783 > ZL30102QDG (ZARLINK SEMICONDUCTOR INC) T1/E1 Stratum 4/4E Redundant System Clock Synchronizer for DS1/E1 and H.110 PDF資料下載

參數資料

| 型號: | ZL30102QDG |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 通信及網絡 |

| 英文描述: | T1/E1 Stratum 4/4E Redundant System Clock Synchronizer for DS1/E1 and H.110 |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP64 |

| 封裝: | 10 X 10 MM, 1 MM HEIGHT, MS-026ACD, TQFP-64 |

| 文件頁數: | 17/50頁 |

| 文件大?。?/td> | 481K |

| 代理商: | ZL30102QDG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

ZL30102

Data Sheet

17

Zarlink Semiconductor Inc.

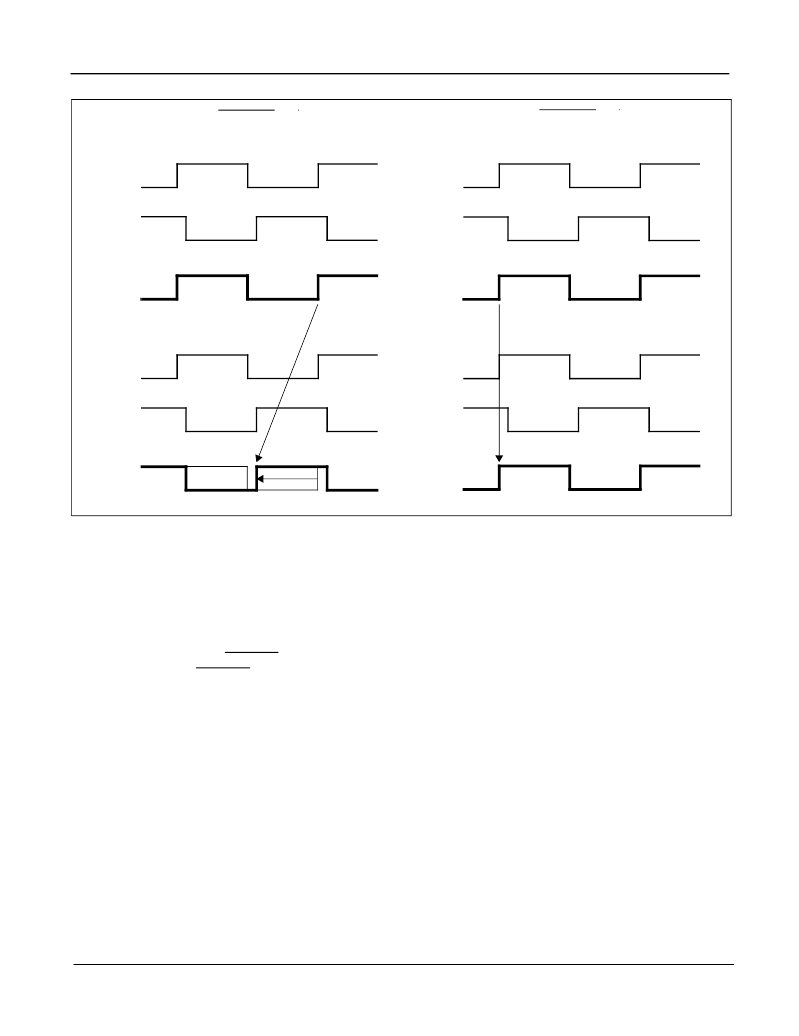

Figure 8 - Timing Diagram of Hitless Reference Switching

The Hitless Mode Switching (HMS) pin enables phase hitless returns from Freerun and Holdover modes to Normal

mode in a single reference operation. A logic low at the HMS input disables the TIE circuit updating the delay value

thereby forcing the output of the PLL to gradually move back to the original point before it went into Holdover mode.

(see Figure 9). This prevents accumulation of phase in network elements. A logic high (HMS=1) enables the TIE

circuit to update its delay value thereby preventing a large output phase movement after return to Normal mode.

This causes accumulation of phase in network elements. In both cases the PLL’s output can be aligned with the

input reference by setting TIE_CLR low. Regardless of the HMS pin state, reference switching in the ZL30102 is

always hitless unless TIE_CLR is kept low continuously.

locked to REF1

REF0

Output

Clock

TIE_CLR = 1

TIE_CLR = 0

REF1

REF0

Output

Clock

REF1

locked to REF1

REF0

Output

Clock

REF1

REF0

Output

Clock

REF1

locked to REF0

locked to REF0

相關PDF資料 |

PDF描述 |

|---|---|

| ZL30105QDG1 | T1/E1/SDH Stratum 3 Redundant System Clock Synchronizer for AdvancedTC TM and H.110 |

| ZL30105 | Power Clamp On Multimeter; DMM Type:Clamp; No. of Digits/Alpha:3-3/4; DMM Response Type:True RMS; Approval Categories:CAT III 600V; Calibrated:No; Current Measuring Range:0-400.0A; Current Setting AC:400A RoHS Compliant: NA |

| ZL30105QDG | Digital Clamp-On Meter; DMM Type:Clamp; No. of Digits/Alpha:3-3/4; DMM Response Type:True RMS; Calibrated:No; Current Setting AC:1000A; Resistance Measuring Range:400 Ohm to 10 MOhm; Voltage Measuring Range AC:600V RoHS Compliant: NA |

| ZL30106QDG1 | SONET/SDH/PDH Network Interface DPLL |

| ZL30106 | SONET/SDH/PDH Network Interface DPLL |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ZL30102QDG1 | 制造商:Microsemi Corporation 功能描述:PB FREE T1/E1 SYSTEM SYNCHRONIZER - Trays 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE T1/E1 SYSTEM SYNCHRONIZER - Trays |

| ZL30105 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:T1/E1/SDH Stratum 3 Redundant System Clock Synchonizer for AdvancedTCA and H.110 |

| ZL30105_05 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:T1/E1/SDH Stratum 3 Redundant System Clock Synchronizer for AdvancedTC TM and H.110 |

| ZL30105QDG | 制造商:Zarlink Semiconductor Inc 功能描述:CLOCK SYNTHESIZER 64TQFP - Bulk |

| ZL30105QDG1 | 制造商:Microsemi Corporation 功能描述:CLOCK SYNTHESIZER 64TQFP - Trays 制造商:Microsemi Corporation 功能描述:IC Pb Free T1/E1 System Synchronizer 制造商:Zarlink Semiconductor Inc 功能描述:CLOCK SYNTHESIZER 64TQFP - Trays 制造商:Zarlink Semiconductor Inc 功能描述:IC Pb Free T1/E1 System Synchronizer |

發(fā)布緊急采購,3分鐘左右您將得到回復。