- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371386 > 240VA (Lattice Semiconductor Corporation) In-System Programmable 3.3V Generic Digital CrosspointTM PDF資料下載

參數(shù)資料

| 型號(hào): | 240VA |

| 廠商: | Lattice Semiconductor Corporation |

| 英文描述: | In-System Programmable 3.3V Generic Digital CrosspointTM |

| 中文描述: | 在系統(tǒng)可編程3.3V的通用數(shù)字CrosspointTM |

| 文件頁(yè)數(shù): | 3/25頁(yè) |

| 文件大?。?/td> | 324K |

| 代理商: | 240VA |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)

3

Specifications

ispGDX240VA

ADVANCED

Architecture

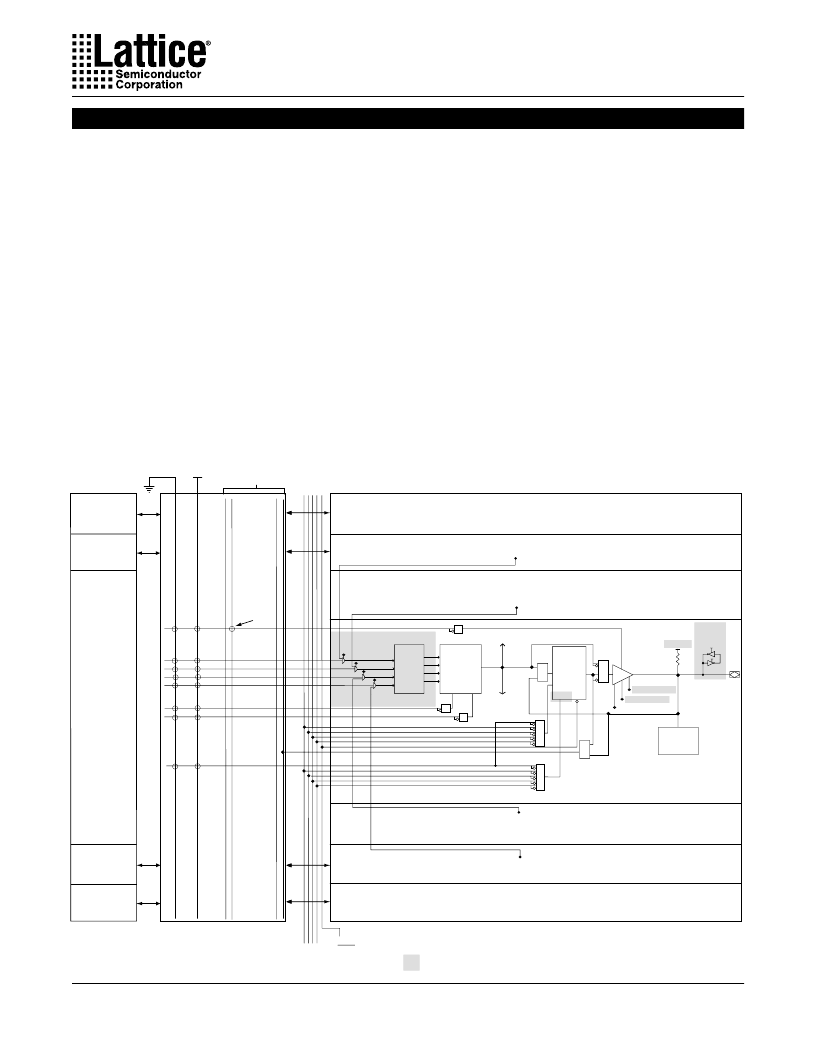

The ispGDXVA architecture is different from traditional

PLD architectures, in keeping with its unique application

focus. The block diagram is shown below. The program-

mable interconnect consists of a single Global Routing

Pool (GRP). Unlike ispLSI devices, there are no pro-

grammable logic arrays on the device. Control signals for

OEs, Clocks/Clock Enables and MUX Controls must

come from designated sets of I/O pins. The polarity of

these signals can be independently programmed in each

I/O cell.

Each I/O cell drives a unique pin. The OE control for each

I/O pin is independent and may be driven via the GRP by

one of the designated I/O pins (I/O-OE set). The I/O-OE

set consists of 25% of the total I/O pins. Boundary Scan

test is supported by dedicated registers at each I/O pin.

In-system programming is accomplished through the

standard Boundary Scan protocol.

The various I/O pin sets are also shown in the block

diagram below. The A, B, C, and D I/O pins are grouped

together with one group per side.

I/O Architecture

Each I/O cell contains a 4:1 dynamic MUX controlled by

two select lines as well as a 4x4 crossbar switch con-

trolled by software for increased routing flexiability (Figure

and M3) come from I/O signals in the GRP and/or

adjacent I/O cells. Each MUX data input can access one

quarter of the total I/Os. For example, in a 240-I/O

ispGDXVA, each data input can connect to one of 60 I/O

pins. MUX0 and MUX1 can be driven by designated I/O

pins called MUXsel1 and MUXsel2. Each MUXsel input

covers 25% of the total I/O pins (e.g. 60 out of 240). MUX0

and MUX1 can be driven from either MUXsel1 or MUXsel2.

Figure 1. ispGDXVA I/O Cell and GRP Detail (240 I/O Device)

I/OCell 0

I/O Cell 1

I/O Cell 118

I/O Cell 119

120 I/O Cells

Boundary

Scan Cell

Bypass Option

I/O Cell N

Register

or Latch

I/O

Pin

Prog.

(VCCIO)

Prog. Slew Rate

CLK

B

Reset

Q

4-to-1 MUX

M0

M1

M2

M3

MUX0

240 Input GRP

Outputs Horizontal

I/O Cell 239

I/O Cell 238

I/O Cell 121

I/O Group A

I/O Group B

I/O Group C

I/O Group D

4x4

Crossbar

Switch

MUX1

Global

Reset

I/O Cell 120

120 I/O Cells

ispGDXVA architecture enhancements over ispGDX (5V)

2

CMOS

Programmable

Interconnect

Logic

“

0

”

Logic

“

1

”

240 I/O Inputs

R

ClocY0-Y3

BProg.

Latch

CLK_EN

From MUX Outputs

of 2 Adjacent I/O Cells

From MUX Outputs

To 2 Adjacent

I/O Cells above

To 2 Adjacent

Prog. Open Drain

2.5V/3.3V Output

N+1

N+2

N-1

N-2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 241101 | USB PANEL SOCKET PCB TYPE B |

| 241102 | USB PANEL SOCKET PCB TYPE B |

| 2412F | MESSUHR BEREICH 0.4ZOLL STOSSFEST LEICHT |

| 2413.2433 | LED MODULE RECTANGULAR RED |

| 2413.2434 | LED MODULE RECTANGULAR RED |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 240x | 制造商:LIGHTING COMP DESIGN 功能描述: 制造商:Lighting Components & Design Inc 功能描述: |

| 240X10019X | 制造商:Conec Corporation 功能描述: |

| 240X10049X | 功能描述:D-Sub工具與硬件 37 POS FERRITE BLOCK RoHS:否 制造商:3M Electronic Solutions Division 產(chǎn)品:Accessories 類型:Strain Relief, 36 Position 用于:Wiremount D-Sub Connectors |

| 240X180X150 | 制造商:ELSTEEL 功能描述:WALL BOX L240XH180XW150MM |

| 240Y | 功能描述:存儲(chǔ)箱與外殼 4-7/8 x 8-7/8 x 3-7/8 Yellow RoHS:否 制造商:Tektronix 顏色:Black 材料:Polypropylene 尺寸:23.25 in L x 20.75 in W x 9 in H |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。