- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371415 > 272420-007 (Intel Corp.) Intel386 EX Embedded Microprocessor PDF資料下載

參數(shù)資料

| 型號: | 272420-007 |

| 廠商: | Intel Corp. |

| 英文描述: | Intel386 EX Embedded Microprocessor |

| 中文描述: | 英特爾386防爆嵌入式微處理器 |

| 文件頁數(shù): | 13/56頁 |

| 文件大小: | 766K |

| 代理商: | 272420-007 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

Intel386 EX Embedded Microprocessor

Datasheet

13

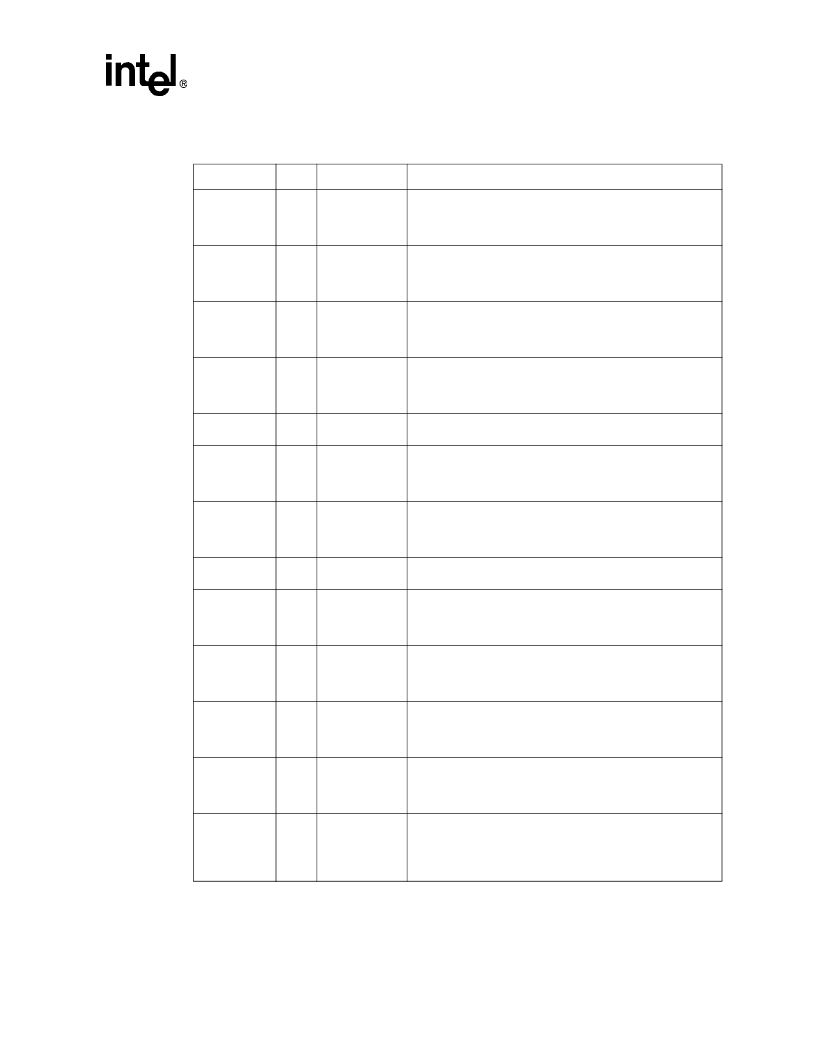

Table 4.

Intel386 EX Microprocessor Pin Descriptions (Sheet 1 of 6)

Symbol

Type

Output States

Name and Function

A25:1

O

H(Z)

R(1)

I(1)

P(1)

Address Bus

outputs physical memory or port I/O addresses.

These signals are valid when ADS# is active and remain valid

until the next T1, T2P, or Ti. During HOLD cycles they are driven

to a high-impedance state. A18:16 are multiplexed with CAS2:0.

ADS#

O

H(Z)

R(1)

I(1)

P(1)

Address Status

indicates that the processor is driving a valid

bus-cycle definition and address (W/R#, D/C#, M/IO#, A25:1,

BHE#, BLE#) onto its pins.

BHE#

O

H(Z)

R(0)

I(X)

P(0)

Byte High Enable

indicates that the processor is transferring a

high data byte.

BLE#

O

H(Z)

R(0)

I(X)

P(1)

Byte Low Enable

indicates that the processor is transferring a

low data byte.

BS8#

I

Bus Size

indicates that an 8-bit device is currently being

addressed.

BUSY#

I

Busy

indicates that the math coprocessor is busy. If BUSY# is

sampled LOW at the falling edge of RESET, the processor

performs an internal self test. BUSY# is multiplexed with

TMRGATE2 and has a temporary weak pull-up resistor.

CAS2:0

O

H(Z)

R(1)

I(1)

P(1)

Cascade Address

carries the slave address information from

the 8259A master interrupt module during interrupt acknowledge

bus cycles. CAS2:0 are multiplexed with A18:16.

CLK2

ST

Clock Input

is connected to an external clock that provides the

fundamental timing for the device.

CLKOUT

O

H(Q)

R(Q)

I(Q)

P(0)

CLKOUT

is a PH1P clock output.

COMCLK

I

Serial Communications Baud Clock

is an alternate clock

source for the asynchronous serial ports. COMCLK is

multiplexed with P3.7 and has a temporary weak pull-down

resistor.

CS4:0#

O

H(1)

R(WH)

I(Q)

P(X)

Chip-selects

are activated when the address of a memory or I/O

bus cycle is within the address region programmed by the user.

They are multiplexed as follows: CS6# with REFRESH#, CS5#

with DACK0#, and CS4:0# with P2.4:0.

CS6:5#

O

H(1)

R(1)

I(Q)

P(X)

Chip-selects

are activated when the address of a memory or I/O

bus cycle is within the address region programmed by the user.

They are multiplexed as follows: CS6# with REFRESH#, CS5#

with DACK0#, and CS4:0# with P2.4:0.

CTS1:0#

I

Clear to Send SIO1 and SIO0

prevent the transmission of data

to the asynchronous serial port’s RXD1 and RXD0 pins,

respectively. CTS1# is multiplexed with EOP#, and CTS0# is

multiplexed with P2.7. CTS1# requires an external pull-up

resistor. Both have temporary weak pull-up resistors.

NOTES:

1. X if clock source is internal; Q if clock source is external

2. Q if JTAG unit is shifting out data, Z if it is not

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 2729-170 | 170 Watts, 38 Volts, 100祍, 10% Radar 2700-2900 MHz |

| 2731-100M | 100 Watts, 36 Volts, 200us, 10% Radar 2700-3100 MHz |

| 2732 | MOS Memory Products |

| 273F06PP481R | POLYPROPYLENE-FOIL SELF CASED AXIAL LEADS |

| 273K06PP580R | POLYPROPYLENE-FOIL SELF CASED AXIAL LEADS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 2724229 | 制造商:Phoenix Contact 功能描述:IBS ELR COV P-6A |

| 272423-000 | 功能描述:焊料和屏蔽管 CWT-9 RoHS:否 制造商:TE Connectivity / Raychem 類型:Shield Terminators 材料:Polyvinylidene Fluoride 內(nèi)徑:5.08 mm 長度:16.5 mm 最低收縮溫度: 系列:S03 |

| 2724232 | 制造商:Phoenix Contact 功能描述:IBS ELR COV W-6A |

| 2724245 | 制造商:Phoenix Contact 功能描述:IBS ELR COV 2-6A |

| 272-425A | 制造商:LG Corporation 功能描述:KNOBVOL/EQ, CFX-425A US1, TW |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。