- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄67319 > 5962-0050401QYC (E2V TECHNOLOGIES PLC) 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, QFP68 PDF資料下載

參數(shù)資料

| 型號(hào): | 5962-0050401QYC |

| 廠商: | E2V TECHNOLOGIES PLC |

| 元件分類(lèi): | ADC |

| 英文描述: | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, QFP68 |

| 封裝: | QFP-68 |

| 文件頁(yè)數(shù): | 53/57頁(yè) |

| 文件大小: | 1276K |

| 代理商: | 5962-0050401QYC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)當(dāng)前第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)

Rev.2.10

Oct 25, 2006

Page 57 of 326

REJ03B0152-0210

M306H7MG-XXXFP/MC-XXXFP/FGFP

6. INTERRUPTS

6.16

INT Interrupt

INTi interrupt (i = 0 to 5) is triggered by the edges of external inputs. The edge polarity is selected using the IFSR

register's IFSRi bit.

INT4 and INT5 share the interrupt vector and interrupt control register with SI/O3 and SI/O4, respectively.

To use the INT4 interrupt, set the IFSR register’s IFSR6 bit to “1” (= INT4). To use the INT5 interrupt, set the IFSR

register’s IFSR7 bit to “1” (= INT5).

After modifying the IFSR6 or IFSR7 bit, clear the corresponding IR bit to “0” (= interrupt not requested) before

enabling the interrupt.

INT2 and the remote control transmission, the vector and the interrupt control register are shared. (Please refer to

“14. Expansion Function” for details. )

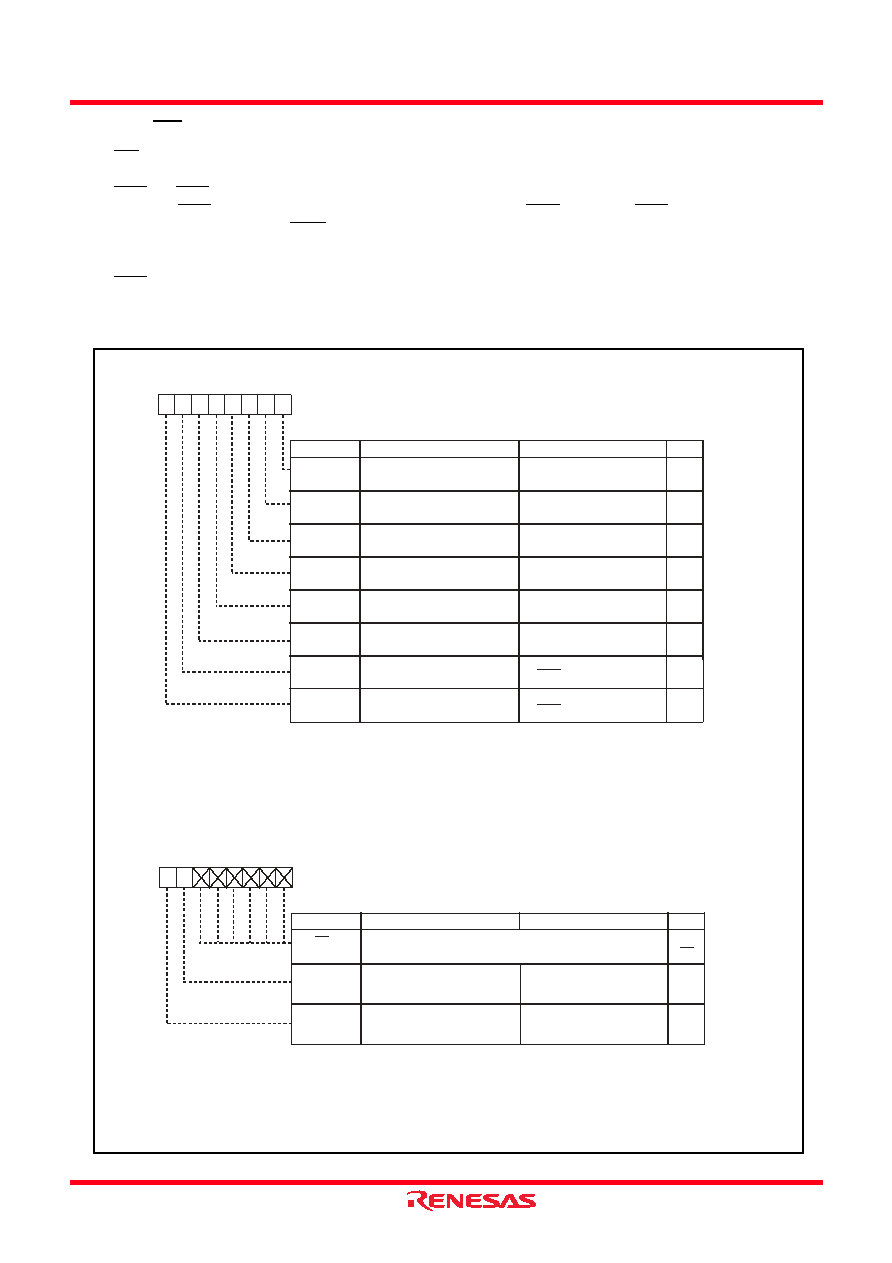

Figure 6.10 shows the IFSR and IFSR2A registers.

Figure 6.10

IFSR Register and IFSR2A Register

Interrupt request cause select register

Bit name

Function

Bit symbol

RW

Symbol

Address

After reset

Symbol

Address

After reset

IFSR

035F16

0016

IFSR0

b7

b6

b5

b4

b3

b2

b1

b0

INT0 interrupt polarity

switching bit

0 : SI/O3

1 : INT4

0 : SI/O4

1 : INT5

0 : One edge

1 : Both edges

0 : One edge

1 : Both edges

0 : One edge

1 : Both edges

0 : One edge

1 : Both edges

0 : One edge

1 : Both edges

INT1 interrupt polarity

switching bit

INT2 interrupt polarity

switching bit

INT3 interrupt polarity

switching bit

INT4 interrupt polarity

switching bit

INT5 interrupt polarity

switching bit

0 : One edge

1 : Both edges

Interrupt request cause

select bit

Interrupt request cause

select bit

IFSR1

IFSR2

IFSR3

IFSR4

IFSR5

IFSR6

IFSR7

RW

(Note 1)

(Note 2)

Note 1: When setting this bit to “1” (= both edges), make sure the INT0IC to INT5IC register’s POL bit

is set to “0” (= falling edge).

Note 2: When setting this bit to “0” (= SI/O3, SI/O4), make sure the S3IC and S4IC registers’ POL bit is

set to “0” (= falling edge).

(Note 2)

Interrupt request cause select register 2

Bit name

Function

Bit symbol

RW

IFSR2A

035E16

00XXXXXX2

b7

b6

b5

b4

b3

b2

b1

b0

0 : Timer B3/HINT

1 : UART0 bus collision

detection

0 : Timer B4/Remote control

1 : UART1 bus collision

detection

IFSR26

IFSR27

Interrupt request cause

select bit (Note 1)

Interrupt request cause

select bit (Note 2)

RW

(b5-b0)

Nothing is assigned. When write, set to “0”.

When read, their contents are indeterminate.

Note 1: Timer B3/HINT and UART0 bus collision detection share the vector and interrupt control register. When using

the timer B3/HINT interrupt, clear the IFSR26 bit to “0” (timer B3/HINT). When using UART0 bus collision

detection, set the IFSR26 bit to “1”.

Note 2: Timer B4/Remote control and UART1 bus collision detection share the vector and interrupt control register.

When using the timer B4/Remote control interrupt, clear the IFSR27 bit to “0” (timer B4/Remote control).

When using UART1 bus collision detection, set the IFSR27 bit to “1”.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962-0050401QYC | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| 5962-0050401QXC | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, QFP68 |

| 5962-0050401QXC | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| 5962-0051101NXD | 1-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

| THS1401CPFB | 1-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-0050601Q2A | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:QUADRUPLE 2-LINE TO 1-LINE DATA SELECTORS/MULTIPLEXERS |

| 5962-0050601QEA | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:QUADRUPLE 2-LINE TO 1-LINE DATA SELECTORS/MULTIPLEXERS |

| 5962-0050601QFA | 制造商:Texas Instruments 功能描述: |

| 5962005066345 | 制造商:Texas Instruments 功能描述: |

| 5962005066346 | 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。