- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378210 > 80960CF (Intel Corp.) 32-Bit High-Performance Superscalar Processor(32位高性能超標量處理器) PDF資料下載

參數(shù)資料

| 型號: | 80960CF |

| 廠商: | Intel Corp. |

| 英文描述: | 32-Bit High-Performance Superscalar Processor(32位高性能超標量處理器) |

| 中文描述: | 32位高性能超標量處理器(32位高性能超標量處理器) |

| 文件頁數(shù): | 35/62頁 |

| 文件大小: | 999K |

| 代理商: | 80960CF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

SPECIAL ENVIRONMENT 80960CF-30, -25, -16

5.0

RESET, BACKOFF AND HOLD

ACKNOWLEDGE

The following table lists the condition of each proc-

essor output pin while RESET is asserted (low).

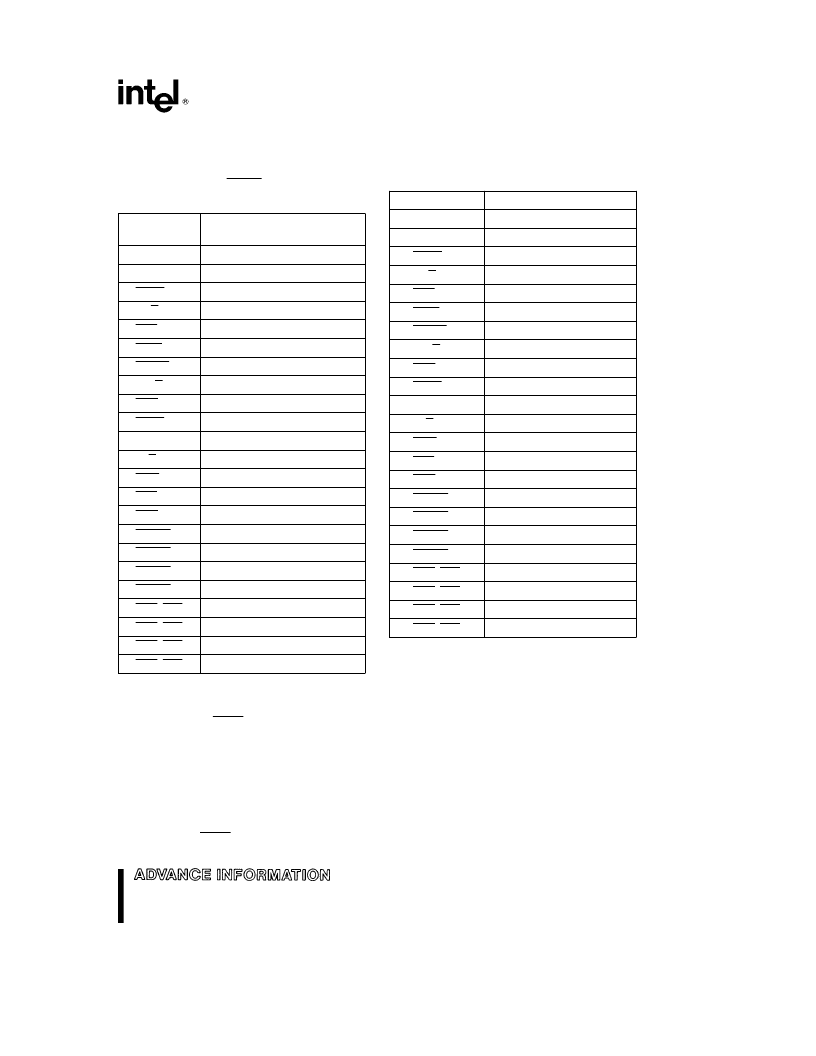

Table 10. Reset Conditions

Pins

State During Reset

(HOLDA inactive)

1

A31:A2

Floating

D31:D0

Floating

BE3:0

Driven high (Inactive)

W/R

Driven low (Read)

ADS

Driven high (Inactive)

WAIT

Driven high (Inactive)

BLAST

Driven low (Active)

DT/R

Driven low (Receive)

DEN

Driven high (Inactive)

LOCK

Driven high (Inactive)

BREQ

Driven low (Inactive)

D/C

Floating

DMA

Floating

SUP

Floating

FAIL

Driven low (Active)

DACK3

Driven high (Inactive)

DACK2

Driven high (Inactive)

DACK1

Driven high (Inactive)

DACK0

Driven high (Inactive)

EOP/TC3

Floating (set to input mode)

EOP/TC2

Floating (set to input mode)

EOP/TC1

Floating (set to input mode)

EOP/TC0

Floating (set to input mode)

NOTE:

(1) With regard to bus output pin state only, the Hold Ac-

knowledge state takes precedence over the reset state. Al-

though asserting the RESET pin will internally reset the

processor, the processor’s bus output pins will not enter

the reset state if it has granted Hold Acknowledge to a pre-

vious HOLD request (HOLDA is active). Furthermore, the

processor will grant new HOLD requests and enter the

Hold Acknowledge state even while in reset.

For example, if HOLDA is not active and the processor is

in the reset state, then HOLD is asserted, the processor’s

bus pins will enter the Hold Acknowledge state and

HOLDA will be granted. The processor will not be able to

perform memory accesses until the HOLD request is re-

moved, even if the RESET pin is brought high. This opera-

tion is provided to simplify boot-up synchronization among

multiple processors sharing the same bus.

The following table lists the condition of each proc-

essor output pin while HOLDA is asserted (low).

Table 11. Hold Acknowledge

and Backoff Conditions

Pins

State During HOLDA

A31:A2

Floating

D31:D0

Floating

BE3:0

Floating

W/R

Floating

ADS

Floating

WAIT

Floating

BLAST

Floating

DT/R

Floating

DEN

Floating

LOCK

Floating

BREQ

Driven (high or low)

D/C

Floating

DMA

Floating

SUP

Floating

FAIL

Driven high (Inactive)

DACK3

Driven high (Inactive)

DACK2

Driven high (Inactive)

DACK1

Driven high (Inactive)

DACK0

Driven high (Inactive)

EOP/TC3

Driven if output

EOP/TC2

Driven if output

EOP/TC1

Driven if output

EOP/TC0

Driven if output

35

相關PDF資料 |

PDF描述 |

|---|---|

| 80960JD | EMBEDDED 32-BIT MICROPROCESSOR |

| 80960JT | EMBEDDED 32-BIT MICROPROCESSOR |

| 80960JF | 3.3 V EMBEDDED 32-BIT MICROPROCESSOR |

| 80960 | 3.3 V EMBEDDED 32-BIT MICROPROCESSOR |

| 80960CA-16 | SPECIAL ENVIRONMENT 80960CA-25, -16 32-BIT HIGH-PERFORMANCE EMBEDDED PROCESSOR |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 80960CF-16 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:80960CF-40, -33, -25, -16 32-BIT HIGH-PERFORMANCE SUPERSCALAR EMBEDDED MICROPROCESSOR |

| 80960CF-25 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:80960CF-40, -33, -25, -16 32-BIT HIGH-PERFORMANCE SUPERSCALAR EMBEDDED MICROPROCESSOR |

| 80960CF-30 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:SPECIAL ENVIRONMENT 80960CF-30, -25, -16 32-BIT HIGH-PERFORMANCE SUPERSCALAR PROCESSOR |

| 80960CF-33 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:80960CF-40, -33, -25, -16 32-BIT HIGH-PERFORMANCE SUPERSCALAR EMBEDDED MICROPROCESSOR |

| 80960CF-40 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:80960CF-40, -33, -25, -16 32-BIT HIGH-PERFORMANCE SUPERSCALAR EMBEDDED MICROPROCESSOR |

發(fā)布緊急采購,3分鐘左右您將得到回復。