- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378211 > 80960RN (Intel Corp.) 80960RN I/O Processor(80960RN I/O 處理器) PDF資料下載

參數(shù)資料

| 型號: | 80960RN |

| 廠商: | Intel Corp. |

| 英文描述: | 80960RN I/O Processor(80960RN I/O 處理器) |

| 中文描述: | 80960RN I / O處理器(80960RN的I / O處理器) |

| 文件頁數(shù): | 22/54頁 |

| 文件大?。?/td> | 851K |

| 代理商: | 80960RN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

80960RN

—

Data Sheet

22

Advance Information

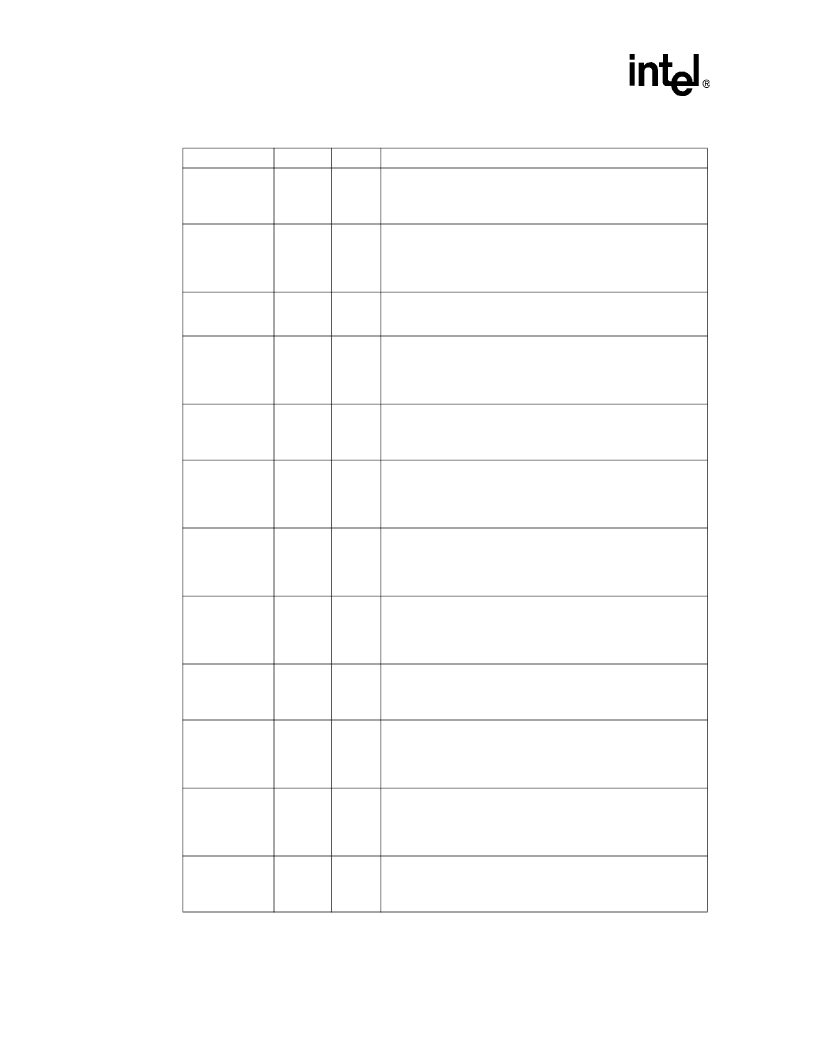

Table 7.

Secondary PCI Bus Signals (Sheet 1 of 2)

NAME

COUNT

TYPE

DESCRIPTION

S_AD[31:0]

32

I/O

5V

Sync(P)

Srst(0)

SECONDARY PCI ADDRESS/DATA

is the multiplexed secondary

PCI address and lower 32 bits of the data bus.

S_AD[63:32]

32

I/O

5V

Sync(P)

Srst(Z)

S32(H)

SECONDARY PCI DATA

is the upper 32 bits of the secondary PCI

data bus.

S_PAR

1

I/O

Sync(P)

Srst(0)

SECONDARY PCI BUS PARITY

is even parity across

S_AD[31:0]

and

S_C/BE[3:0]#

.

S_PAR64

1

I/O

5V

Sync(P)

Srst(Z)

S32(H)

SECONDARY PCI BUS UPPER DWORD PARITY

is even parity

across

S_AD[63:32]

and

S_C/BE[7:4]#

.

S_C/BE[3:0]#

4

I/O

5V

Sync(P)

Srst(0)

SECONDARY PCI BUS COMMAND and BYTE ENABLES

are

multiplexed on the same PCI pins. During the address phase, they

define the bus command. During the data phase, they are used as

the byte enables for

S_AD[31:0]

.

S_C/BE[7:4]#

4

I/O

5V

Sync(P)

Srst(Z)

S32(H)

SECONDARY PCI BYTE ENABLES

are used as byte enables for

S_AD[63:32]

during secondary PCI data phases.

S_REQ64#

1

I/O

5V

Sync(P)

Srst(Q)

S32(Z)

SECONDARY PCI BUS REQUEST 64-BIT TRANSFER

indicates

the attempt of a 64-bit transaction on the secondary PCI bus. If the

target is 64-bit capable, the target acknowledges the attempt with

the assertion of

S_ACK64#

.

S_ACK64#

1

I/O

5V

Sync(P)

Srst(Z)

S32(Z)

SECONDARY PCI BUS ACKNOWLEDGE 64-BIT TRANSFER

indicates that the device has positively decoded its address as the

target of the current access, indicates the target is willing to transfer

data using 64 bits.

S_FRAME#

1

I/O

5V

Sync(P)

Srst(Z)

SECONDARY PCI BUS CYCLE FRAME

is asserted to indicate the

beginning and duration of an access.

S_IRDY#

1

I/O

5V

Sync(P)

Srst(Z)

SECONDARY PCI BUS INITIATOR READY

indicates the initiating

agent

’

s ability to complete the current data phase of the

transaction. During a write, it indicates that valid data is present on

the secondary Address/Data bus. During a read, it indicates the

processor is ready to accept the data.

S_TRDY#

1

I/O

5V

Sync(P)

Srst(Z)

SECONDARY PCI BUS TARGET READY

indicates the target

agent

’

s ability to complete the current data phase of the

transaction. During a read, it indicates that valid data is present on

the secondary Address/Data bus. During a write, it indicates the

target is ready to accept the data.

S_STOP#

1

I/O

5V

Sync(P)

Srst(Z)

SECONDARY PCI BUS STOP

indicates a request to stop the

current transaction on the secondary PCI bus.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 80960SA | Embedded 32-Bit Microprocessor With 16-Bit Burst Data Bus(帶有16位脈沖串數(shù)據(jù)總線的嵌入式 32-BIT微處理器) |

| 80960SB | Embedded 32-Bit Microprocessor With 16-Bit Burst Data Bus(帶有16位脈沖串數(shù)據(jù)總線的嵌入式 32-BIT微處理器) |

| 8097JF | COMMERCIAL/EXPRESS HMOS MICROCONTOLLER |

| 8098 | COMMERCIAL/EXPRESS HMOS MICROCONTROLLER |

| 8098 | T-1 Subminiature Lamps |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 80960SA | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:EMBEDDED 32-BIT MICROPROCESSOR WITH 16-BIT BURST DATA BUS |

| 80960SB | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:EMBEDDED 32-BIT MICROPROCESSOR WITH 16-BIT BURST DATA BUS |

| 80961-01 | 制造商:Glenair 功能描述:EARTH BOND M10 FOR AL 4MM T |

| 809621-000 | 制造商:TE Connectivity 功能描述:809621-000 |

| 80963 | 制造商:3M Electronic Products Division 功能描述:Tape Temflex 1500 Brown 15mmx10m |

發(fā)布緊急采購,3分鐘左右您將得到回復。