- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378217 > 82801E (INTEL CORP) Intel 82801E Communications I/O Controller Hub (C-ICH) PDF資料下載

參數(shù)資料

| 型號(hào): | 82801E |

| 廠商: | INTEL CORP |

| 元件分類: | 外設(shè)及接口 |

| 英文描述: | Intel 82801E Communications I/O Controller Hub (C-ICH) |

| 中文描述: | MULTIFUNCTION PERIPHERAL, PBGA421 |

| 封裝: | BGA-421 |

| 文件頁(yè)數(shù): | 41/84頁(yè) |

| 文件大小: | 1196K |

| 代理商: | 82801E |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)當(dāng)前第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)

Intel

82801E C-ICH

Advance Information Datasheet

41

3.2.7

LPC Interface

3.2.8

Interrupt Interface

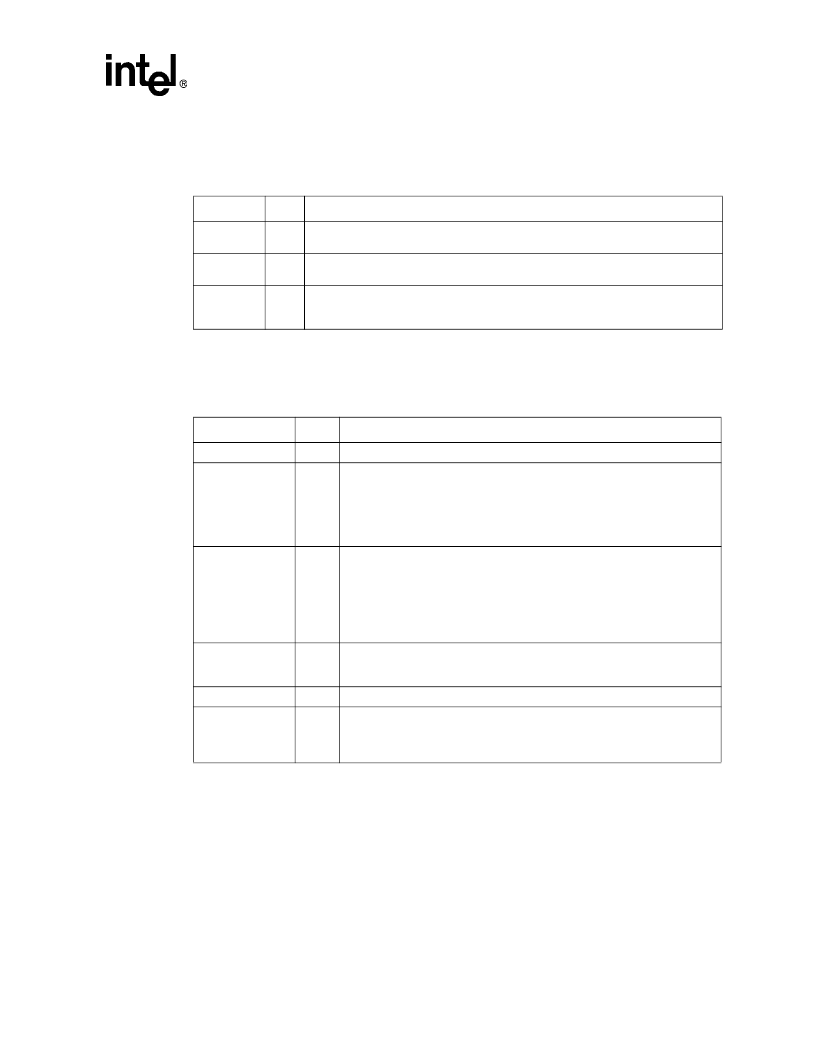

Table 13. LPC Interface Signals

Name

Type

Description

LAD[3:0]

/FWH[3:0]

I/O

LPC Multiplexed Command, Address, Data:

Internal pull-ups are provided.

LFRAME#

/FWH[4]

O

LPC Frame:

LFRAME# indicates the start of an LPC cycle, or an abort.

LDRQ[1:0]#

I

LPC Serial DMA/Master Request Inputs:

These signals are used to request DMA or

bus master access. Typically, they are connected to external Super I/O device. An

internal pull-up resistor is provided on these signals.

Table 14. Interrupt Signals

Name

Type

Description

SERIRQ

I/O

Serial Interrupt Request:

This pin implements the serial interrupt protocol.

PIRQ[A:D]#

I/OD

PCI Interrupt Requests:

In Non-APIC Mode the PIRQx# signals can be routed

to interrupts 3:7, 9:12, 14, or 15 as described in the Interrupt Steering section.

Each PIRQx# line has a separate Route Control Register.

In APIC mode, these signals are connected to the internal I/O APIC in the

following fashion: PIRQ[A]# is connected to IRQ16, PIRQ[B]# to IRQ17,

PIRQ[C]# to IRQ18, and PIRQ[D]# to IRQ19. This frees the ISA interrupts.

PIRQ[E:F]#

PIRQ[G]#/GPIO[4]

PIRQ[H]#/GPIO[5]

I/OD

PCI Interrupt Requests:

In Non-APIC Mode the PIRQx# signals can be routed

to interrupts 3:7, 9:12, 14 or 15 as described in the Interrupt Steering section.

Each PIRQx# line has a separate Route Control Register.

In APIC mode, these signals are connected to the internal I/O APIC in the

following fashion: PIRQ[E]# is connected to IRQ20, PIRQ[F]# to IRQ21,

PIRQ[G]# to IRQ22, and PIRQ[H]# to IRQ23. This frees the ISA interrupts. If

not needed for interrupts, PIRQ[H:G] can be used as GPIO.

IRQ[14:15]

I

Interrupt Request 14:15:

These interrupt inputs are connected to the IDE

drives. IRQ14 is used by the drives connected to the primary controller and

IRQ15 is used by the drives connected to the secondary controller.

APICCLK

I

APIC Clock:

The APIC clock runs at 33.333 MHz.

APICD[1:0]

I/OD

APIC Data:

These bidirectional open drain signals are used to send and

receive data over the APIC bus. As inputs, the data is valid on the rising edge

of APICCLK. As outputs, new data is driven from the rising edge of the

APICCLK.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 82802AB | Firmware Hub (FWH) |

| 82802AC | Firmware Hub (FWH) |

| 8281 | LNB SUPPLY AND CONTROL-VOLTAGE REGULATORS |

| 8282 | OCTAL LATCH |

| 8282 | LNB SUPPLY AND CONTROL-VOLTAGE REGULATORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 82801FB | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel I/O Controller Hub 6 (ICH6) Family |

| 82801FBM | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel I/O Controller Hub 6 (ICH6) Family |

| 82801FR | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel I/O Controller Hub 6 (ICH6) Family |

| 82801GBICH7 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel I/O Controller Hub 7 |

| 82801GBMICH7-M | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel I/O Controller Hub 7 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。