- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄36334 > 935260699551 (NXP SEMICONDUCTORS) SPECIALTY CONSUMER CIRCUIT, PQFP208 PDF資料下載

參數(shù)資料

| 型號(hào): | 935260699551 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP208 |

| 封裝: | PLASTIC, SOT-316, SQFP-208 |

| 文件頁(yè)數(shù): | 13/148頁(yè) |

| 文件大小: | 692K |

| 代理商: | 935260699551 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)

1998 Apr 09

11

Philips Semiconductors

Product specication

Multimedia bridge, high performance

Scaler and PCI circuit (SPCI)

SAA7146A

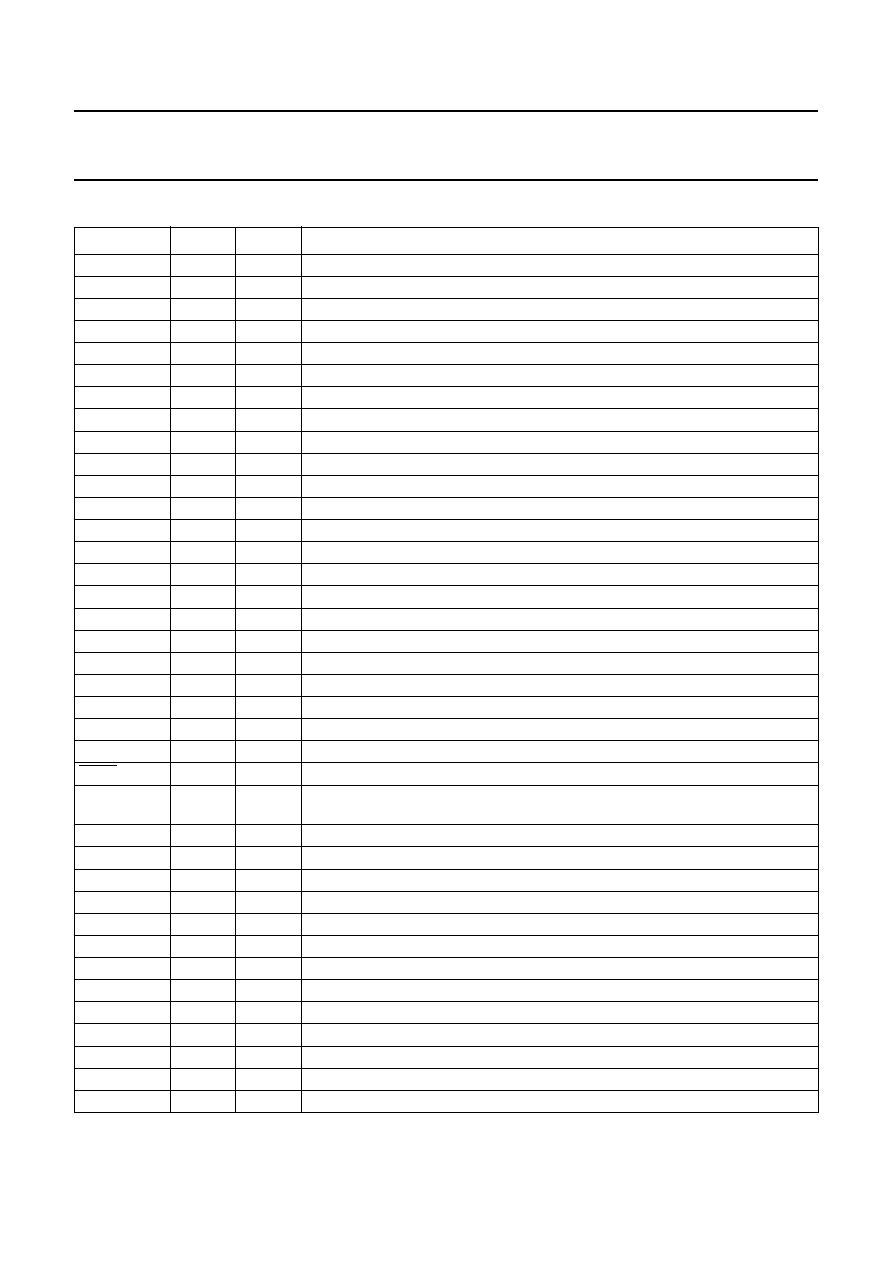

Pin description for SQFP208

SYMBOL

PIN

STATUS

DESCRIPTION

VSSD0

1

P

digital ground 0

D1_A0

2

I/O

bidirectional digital CCIR 656 D1 port A bit 0

D1_A1

3

I/O

bidirectional digital CCIR 656 D1 port A bit 1

D1_A2

4

I/O

bidirectional digital CCIR 656 D1 port A bit 2

D1_A3

5

I/O

bidirectional digital CCIR 656 D1 port A bit 3

VDDD1

6

P

digital supply voltage 1 (3.3 V)

n.c.

7

reserved pin; not connected internally

VSSD1

8

P

digital ground 1

D1_A4

9

I/O

bidirectional digital CCIR 656 D1 port A bit 4

D1_A5

10

I/O

bidirectional digital CCIR 656 D1 port A bit 5

D1_A6

11

I/O

bidirectional digital CCIR 656 D1 port A bit 6

D1_A7

12

I/O

bidirectional digital CCIR 656 D1 port A bit 7

VDDD2

13

P

digital supply voltage 2 (3.3 V)

n.c.

14

reserved pin; not connected internally

VSSD2

15

P

digital ground 2

VS_A

16

I/O

bidirectional vertical sync signal port A

HS_A

17

I/O

bidirectional horizontal sync signal port A

LLC_A

18

I/O

bidirectional line-locked system clock port A

PXQ_A

19

I/O

bidirectional pixel qualier signal to mark valid pixels port A; note 1

n.c.

20

reserved pin; do not connect

VDDD3

21

P

digital supply voltage 3 (3.3 V)

n.c.

22

reserved pin; not connected internally

VSSD3

23

P

digital ground 3

TRST

24

I

test reset input (JTAG pin must be set LOW for normal operation)

TMS

25

I

test mode select input (JTAG pin must be oating or set to HIGH during normal

operation)

TCLK

26

I

test clock input (JTAG pin should be set LOW during normal operation)

TDO

27

O

test data output (JTAG pin not active during normal operation)

TDI

28

I

test data input (JTAG pin must be oating or set to HIGH during normal operation)

VDDD4

29

P

digital supply voltage 4 (3.3 V)

n.c.

30

reserved pin; not connected internally

VSSD4

31

P

digital ground 4

INTA#

32

O

PCI interrupt line output (active LOW)

RST#

33

I

PCI global reset input (active LOW)

CLK

34

I

PCI clock input

GNT#

35

I

bus grant input signal input, PCI arbitration signal (active LOW)

REQ#

36

O

bus request output signal output, PCI arbitration signal (active LOW)

VDDD5

37

P

digital supply voltage 5 (3.3 V)

n.c.

38

reserved pin; not connected internally

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935260699557 | SPECIALTY CONSUMER CIRCUIT, PQFP208 |

| 935243450551 | COLOR SIGNAL ENCODER, PQFP44 |

| 935243450557 | COLOR SIGNAL ENCODER, PQFP44 |

| 935243460551 | COLOR SIGNAL ENCODER, PQFP44 |

| 935243460557 | COLOR SIGNAL ENCODER, PQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935261069122 | 制造商:NXP Semiconductors 功能描述:IC SECURITY TRANSPONDER PLLMC |

| 935262025112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935262217118 | 制造商:NXP Semiconductors 功能描述:Real Time Clock Serial 8-Pin SO T/R |

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。