- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373859 > AD1801 (Analog Devices, Inc.) Single-Chip Fax/Data/ Voice Modem(單片的傳真/數(shù)據(jù)/語音調(diào)制解調(diào)器) PDF資料下載

參數(shù)資料

| 型號: | AD1801 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Single-Chip Fax/Data/ Voice Modem(單片的傳真/數(shù)據(jù)/語音調(diào)制解調(diào)器) |

| 中文描述: | 單芯片傳真/數(shù)據(jù)/語音調(diào)制解調(diào)器(單片的傳真/數(shù)據(jù)/語音調(diào)制解調(diào)器) |

| 文件頁數(shù): | 27/52頁 |

| 文件大小: | 348K |

| 代理商: | AD1801 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

AD1801

–27–

REV. 0

Emulation Mode (EZ-ICE

Port)

Unlike the ADSP-2181, which ignores its normal (non-emulator)

reset pin when in emulator mode, all AD1801 reset sources are

still functional when in emulator mode. This includes the RESET

pin (ISA reset), the

RESET

pin (power-up reset), the RST

(Host PC reset) bit in I/O mapped register PCC, PnP reset, and

PCMCIA reset. As a result, in order to avoid erroneous emula-

tor results, care must be taken to prevent the assertion of any of

these resets during periods of time when the emulator actually

takes control of the DSP core.

The 14-pin EZ-ICE

port interface should be connected to the

AD1801 as indicated below.

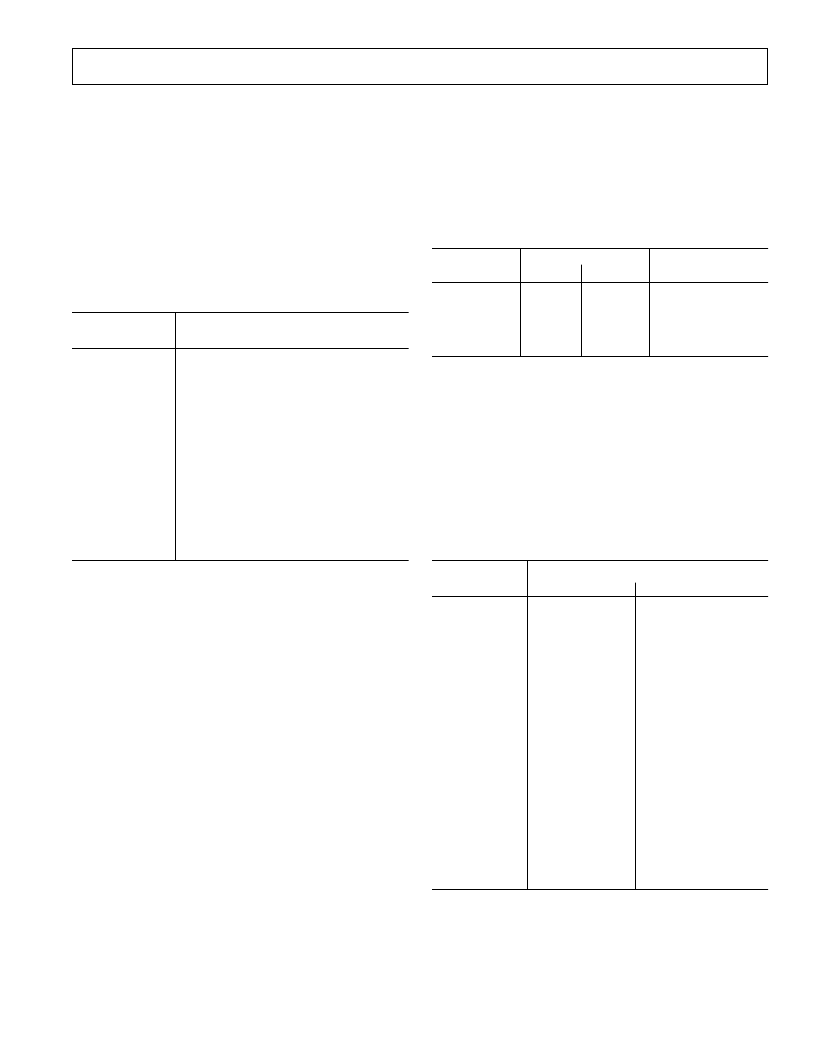

Table VII. Emulator Connections

EZ-ICE

Connector Pin

AD1801 Connection

1 GND

2

BG

3

EBG

4

BR

5

EBR

6

EINT

7 “key”

8 ELIN

9 ELOUT

10 ECLK

11 EE

12

EMS

13

RESET

14

ERESET

Digital GND (Not Analog Supply)

No Connect

EBG

(Pin 30)

Digital V

DD

(Not Analog Supply)

EBR

(Pin 28)

EINT

(Pin 26)

No Connect

ELIN (Pin 25)

ELOUT (Pin 32)

ECLK (Pin 27)

EE (Pin 29)

EMS

(Pin 31)

Digital V

DD

(Not Analog Supply)

ERESET

(Pin 22)

As with the ADSP-2181, all AD1801 emulation pins (Pins 22 and

25–32) should be floated when not connected to the EZ-ICE

port. Within the AD1801 there is a pull-down resistor on the

EE (emulation enable) pin which disables emulation mode when

the EE pin is floated.

Note that the ADSP-2181 chip includes two emulator signals

not found (and not required) on the AD1801

BG

(Bus Grant)

and

BR

(Bus Request). Under normal ADSP-2181 operation,

and external device can interrupt the DSP to use its bus. This is

done with the

BR

and

BG

pins; the external device asserts

BR

,

and the ADSP-2181 asserts

BG

when the bus is available. In the

same scenario with an EZ-ICE in the system, the EZ-ICE takes

the

BR

signal, ORs in its own bus request, and generates

EBR

to the ADSP-2181. The ADSP-2181 then asserts

EBG

, which

the emulator may pass on to the external device as

BG

. During

emulator mode, the ADSP-2181 ignores

BR

and three-states

BG

(so that the emulator can drive it instead). Since the AD1801

does not allow any external devices to be connected to the DSP

core, there is no need for the

BR

and

BG

signals. When using an

emulator,

BR

should be wired deasserted (HI) on the emulator

connector.

PC AND DSP I/O MAPPED REGISTER DESCRIPTIONS

PC I/O Memory Map

The AD1801 bus interface uses the base address determined

during an initialization period to allow host PC access to its

internal registers and ports according to the table below. The

base address will correspond to system address bits SA (15:3)

when the AD1801 is in “ISA” mode and to bits SA (11:3) when

the AD1801 is in “PCMCIA” mode.

Table VIII. PC I/O Memory Map

System Address

Bits SA [11:3]

Resource Accessed

Reads

Writes

Function

Base Addr + 0

PCS

PCC

Host PC Status and

Control

Internal DMA Address

Memory Data I/O

Test Mode

Base Addr + 2

Base Addr + 4

Base Addr + 6

Reserved

MDI

TM

IDMAC

MDO

TM

P

C Attribute Memory Map

Attribute memory space is defined for PCMCIA AD1801 con-

figurations only.

All registers in PCMCIA Attribute Memory Space (0x200

to 0x27F) will read 0 and ignore writes unless specifically

documented.

The AD1801 provides three PCMCIA Functions. Function 0 is

completely contained on the AD1801 chip (i.e., the fax/data/

voice modem), while Functions 1 and 2 are implemented exter-

nally to the AD1801 and are supported with I/O pins.

Table IX. PC Attribute Memory Map

System

Address

Register/RAM Accessed

Name

Valid Operation

0x000–0x3FF

0x400

0x402

0x406

0x408

0x40A

0x40C

0x412

0x440

0x442

0x446

0x44A

0x44C

0x452

0x480

0x482

0x48A

0x48C

0x492

CIS RAM

COR0

CSR0

SCR0

ESR0

IOBL0

IOBH0

IOS0

COR1

CSR1

SCR1

IOBL1

IOBH1

IOS1

COR2

CSR2

IOBL2

IOBH2

IOS2

Read Only

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

Read/Write

EZ-ICE is a registered trademark of Analog Devices, Inc.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD1803JRU | U.S./International Modem DAA Line Codec Chipset |

| AD1803 | ECONOLINE: RD & RC - Dual Output from a Single Input Rail- 1kVDC & 2kVDC Isolation- Power Sharing on Output- Custom Solutions Available- UL94V-0 Package Material- Efficiency to 86% |

| AD1804 | U.S./International Modem DAA Line Codec Chipset |

| AD1804JRU | ECONOLINE: RD & RC - Dual Output from a Single Input Rail- 1kVDC & 2kVDC Isolation- Power Sharing on Output- Custom Solutions Available- UL94V-0 Package Material- Efficiency to 86% |

| AD1812JST | Silver Mica Capacitor; Capacitance:12pF; Capacitance Tolerance: 5%; Series:CD17; Voltage Rating:500VDC; Capacitor Dielectric Material:Mica; Termination:Radial Leaded; Lead Pitch:5.9mm; Leaded Process Compatible:No RoHS Compliant: No |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD1801JS | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AD1801JST-REEL | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| AD1803 | 制造商:AD 制造商全稱:Analog Devices 功能描述:U.S./International Modem DAA Line Codec Chipset |

| AD1803-0.4 | 制造商:Analog Devices 功能描述: |

| AD1803JRU | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。