- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373891 > AD6653-125EBZ (Analog Devices, Inc.) IF Diversity Receiver PDF資料下載

參數(shù)資料

| 型號: | AD6653-125EBZ |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | IF Diversity Receiver |

| 中文描述: | IF分集接收機 |

| 文件頁數(shù): | 30/80頁 |

| 文件大?。?/td> | 1998K |

| 代理商: | AD6653-125EBZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

AD6653

When using the SPI port interface, the user can place the ADC

in power-down mode or standby mode. Standby mode allows

the user to keep the internal reference circuitry powered when

faster wake-up times are required. See the Memory Map Register

Description section and Application Note AN-877,

Interfacing

to High Speed ADCs via SPI

at

www.analog.com

for additional

details.

DIGITAL OUTPUTS

The AD6653 output drivers can be configured to interface with

1.8 V to 3.3 V CMOS logic families by matching DRVDD to the

digital supply of the interfaced logic. Alternatively, the AD6653

outputs can be configured for either ANSI LVDS or reduced

drive LVDS using a 1.8 V DRVDD supply.

In CMOS output mode, the output drivers are sized to provide

sufficient output current to drive a wide variety of logic families.

However, large drive currents tend to cause current glitches on

the supplies that may affect converter performance. Applications

requiring the ADC to drive large capacitive loads or large fanouts

may require external buffers or latches.

The output data format can be selected for either offset binary

or twos complement by setting the SCLK/DFS pin when operating

in the external pin mode (see Table 12). As detailed in Application

Note AN-877,

Interfacing to High Speed ADCs via SPI

, the data

format can be selected for offset binary, twos complement, or

gray code when using the SPI control.

Rev. 0 | Page 30 of 80

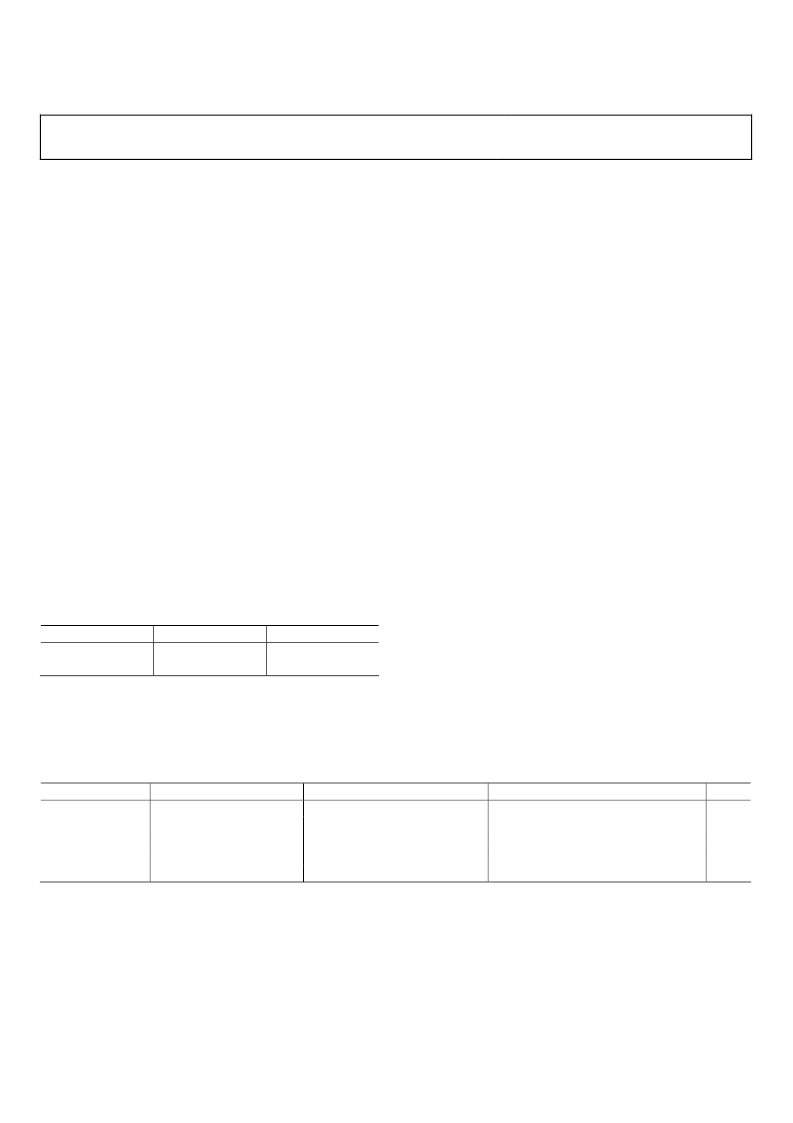

Table 12. SCLK/DFS Mode Selection (External Pin Mode)

Voltage at Pin

SCLK/DFS

AGND (default)

Offset binary

AVDD

Twos complement

SDIO/DCS

DCS disabled

DCS enabled

Digital Output Enable Function (OEB)

The AD6653 has a flexible, three-state ability for the digital output

pins. The three-state modeis enabled using the SMI SDO/OEB

pin or through the SPI interface.

If the SMI SDO/OEB pin is low, the output data drivers are enabled.

If the SMI SDO/OEB pin is high, the output data drivers are placed

in a high impedance state.

This OEB function is not intended for rapid access to the data

bus. Note that OEB is referenced to the digital output driver

supply (DRVDD) and should not exceed that supply voltage.

When using the SPI interface, the data and fast detect outputs of

each channel can be independently three-stated by using the

output enable bar bit, Bit 4 in Register 0x14.

Interleaved CMOS Mode

Setting Bit 5 in Register 0x14 enables interleaved CMOS output

mode. In this mode, output data is routed through Port A with

the ADC Channel A output data present on the rising edge of

DCO and the ADC Channel B output data present on the

falling edge of DCO.

Timing

The AD6653 provides latched data with a pipeline delay that is

dependent on which of the digital back end features are enabled.

Data outputs are available one propagation delay (t

PD

) after the

rising edge of the clock signal.

The length of the output data lines and loads placed on them

should be minimized to reduce transients within the AD6653.

These transients can degrade converter dynamic performance.

The lowest typical conversion rate of the AD6653 is 10 MSPS. At

clock rates below 10 MSPS, dynamic performance may degrade.

Data Clock Output (DCO)

The AD6653 also provides data clock output (DCO) intended for

capturing the data in an external register. Figure 2 through Figure

6

show a graphical timing description of the AD6653 output

modes.

Table 13. Output Data Format

Input (V)

VIN+ – VIN

VIN+ – VIN

VIN+ – VIN

VIN+ – VIN

VIN+ VIN

Condition (V)

< VREF 0.5 LSB

= VREF

= 0

= +VREF 1.0 LSB

> +VREF 0.5 LSB

Offset Binary Output Mode

0000 0000 0000

0000 0000 0000

1000 0000 0000

1111 1111 1111

1111 1111 1111

Twos Complement Mode

1000 0000 0000

1000 0000 0000

0000 0000 0000

0111 1111 1111

0111 1111 1111

OR

1

0

0

0

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD6653BCPZ-125 | IF Diversity Receiver |

| AD6653BCPZ-150 | IF Diversity Receiver |

| AD6655BCPZ-1251 | IF Diversity Receiver |

| AD6655 | IF Diversity Receiver |

| AD6655-125EBZ1 | IF Diversity Receiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6653-150EBZ | 制造商:Analog Devices 功能描述:EVAL BD FOR AD6653 - Bulk |

| AD6653BCPZ-125 | 制造商:Analog Devices 功能描述:IF DIVERSITY RCVR 64LFCSP EP - Trays 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述:IC RECEIVER IF DIVERSITY LFCSP64 |

| AD6653BCPZ-150 | 制造商:Analog Devices 功能描述:IF DIVERSITY RCVR 64LFCSP EP - Trays 制造商:Analog Devices 功能描述:IC RECEIVER IF DIVERSITY LFCSP64 制造商:Analog Devices 功能描述:IC, RECEIVER, IF DIVERSITY, LFCSP64 |

| AD6654 | 制造商:Analog Devices 功能描述:- Bulk |

| AD6654/PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:14-Bit, 92.16 MSPS, 4-/6-Channel Wideband IF to Baseband Receiver |

發(fā)布緊急采購,3分鐘左右您將得到回復。