- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373891 > AD6653 (Analog Devices, Inc.) IF Diversity Receiver PDF資料下載

參數(shù)資料

| 型號(hào): | AD6653 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | IF Diversity Receiver |

| 中文描述: | IF分集接收機(jī) |

| 文件頁(yè)數(shù): | 46/80頁(yè) |

| 文件大小: | 1998K |

| 代理商: | AD6653 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)當(dāng)前第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)

AD6653

Rev. 0 | Page 46 of 80

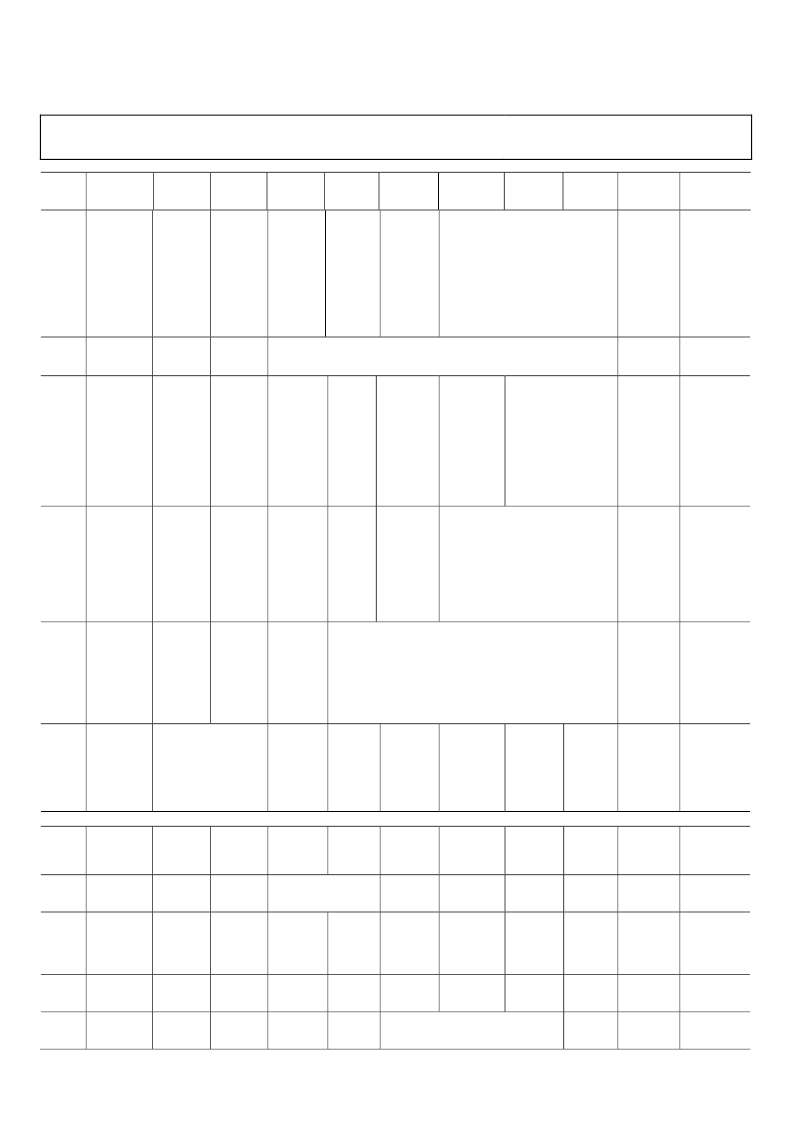

Addr.

(Hex)

0x0D

Register

Name

Test Mode

(Local)

Bit 7

(MSB)

Open

Bit 6

Open

Bit 5

Reset

PN long

sequence

Bit 4

Reset

PN short

sequence

Bit 3

Open

Bit 2

Bit 1

Bit 0

(LSB)

Default

Value

(Hex)

0x00

Default

Notes/

Comments

When

enabled, the

test data is

placed on

the output

pins

in place of

ADC output

data

Output test mode

000 = off (default)

001 = midscale short

010 = positive FS

011 = negative FS

100 = alternating

checkerboard

101 = PN long sequence

110 = PN short sequence

111 = one/zero word toggle

0x10

Offset

Adjust

(Local)

Output Mode

Open

Open

Offset adjust in LSBs from +31 to 32 (twos complement format)

0x00

0x14

Drive

strength

0 V to 3.3 V

CMOS or

ANSI

LVDS

1 V to 1.8 V

CMOS or

reduced

LVDS

(global)

Invert

DCO clock

Output

type

0 = CMOS

1 = LVDS

(global)

Interleaved

CMOS

(global)

Output

enable

bar

(local)

Open

Output

invert

(local)

00 = offset binary

01 = twos complement

01 = gray code

11 = offset binary

(local)

0x00

Configures

the outputs

and the

format of

the data

0x16

Clock Phase

Control

(Global)

Open

Open

Open

Open

Input clock divider phase adjust

000 = no delay

001 = 1 input clock cycle

010 = 2 input clock cycles

011 = 3 input clock cycles

100 = 4 input clock cycles

101 = 5 input clock cycles

110 = 6 input clock cycles

111 = 7 input clock cycles

DCO clock delay

(delay = 2500 ps × register value/31)

00000 = 0 ps

00001 = 81 ps

00010 = 161 ps

…

11110 = 2419 ps

11111 = 2500 ps

Open

Open

0x00

Allows

selection of

clock delays

into the

input clock

divider

0x17

DCO Output

Delay

(Global)

Open

Open

Open

0x00

0x18

VREF Select

(Global)

Reference voltage

selection

00 = 1.25 V p-p

01 = 1.5 V p-p

10 = 1.75 V p-p

11 = 2.0 V p-p

(default)

Open

Open

Open

Open

0xC0

Digital Feature Control Registers

0x100

Sync Control

(Global)

Signal

monitor

sync

enable

Open

Half-band

next sync

only

Half-band

sync

enable

NCO32

next

sync only

NCO32

sync

enable

Clock

divider next

sync only

Clock

divider

sync

enable

f

S

/8 next

sync only

Master

sync

enable

0x00

0x101

f

S

/8 Output

Mix Control

(Global)

FIR Filter

and Output

Mode

Control

(Global)

Open

f

S

/8 start state

Open

Open

f

S

/8 sync

enable

0x00

0x102

Open

Open

Open

Open

FIR gain

0 = gain of

2

1 = gain of

1

Half-band

decimation

phase

f

S

/8 output

mix disable

Complex

output

enable

FIR filter

enable

0x00

0x103

Digital Filter

Control

(Global)

Fast Detect

Control

(Local)

Open

Open

Open

Open

Spectral

reversal

High-pass/

low-pass

select

Open

0x01

0x104

Open

Open

Open

Open

Fast Detect Mode Select[2:0]

Fast

detect

enable

0x00

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD6653-125EBZ | IF Diversity Receiver |

| AD6653BCPZ-125 | IF Diversity Receiver |

| AD6653BCPZ-150 | IF Diversity Receiver |

| AD6655BCPZ-1251 | IF Diversity Receiver |

| AD6655 | IF Diversity Receiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6653-125EBZ | 制造商:Analog Devices 功能描述:Evaluation Board For AD6653 制造商:Analog Devices 功能描述:EVAL BD FOR AD6653 - Bulk 制造商:Analog Devices 功能描述:KIT EVALUATION BOARD AD6653 |

| AD6653-150EBZ | 制造商:Analog Devices 功能描述:EVAL BD FOR AD6653 - Bulk |

| AD6653BCPZ-125 | 制造商:Analog Devices 功能描述:IF DIVERSITY RCVR 64LFCSP EP - Trays 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述:IC RECEIVER IF DIVERSITY LFCSP64 |

| AD6653BCPZ-150 | 制造商:Analog Devices 功能描述:IF DIVERSITY RCVR 64LFCSP EP - Trays 制造商:Analog Devices 功能描述:IC RECEIVER IF DIVERSITY LFCSP64 制造商:Analog Devices 功能描述:IC, RECEIVER, IF DIVERSITY, LFCSP64 |

| AD6654 | 制造商:Analog Devices 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。