- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378286 > ADE7763ARS (ANALOG DEVICES INC) Single-Phase Active and Apparent Energy Metering IC PDF資料下載

參數(shù)資料

| 型號: | ADE7763ARS |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 電源管理 |

| 英文描述: | Single-Phase Active and Apparent Energy Metering IC |

| 中文描述: | 2-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO20 |

| 封裝: | MO-150AE, SSOP-20 |

| 文件頁數(shù): | 17/56頁 |

| 文件大?。?/td> | 1328K |

| 代理商: | ADE7763ARS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

ADE7763

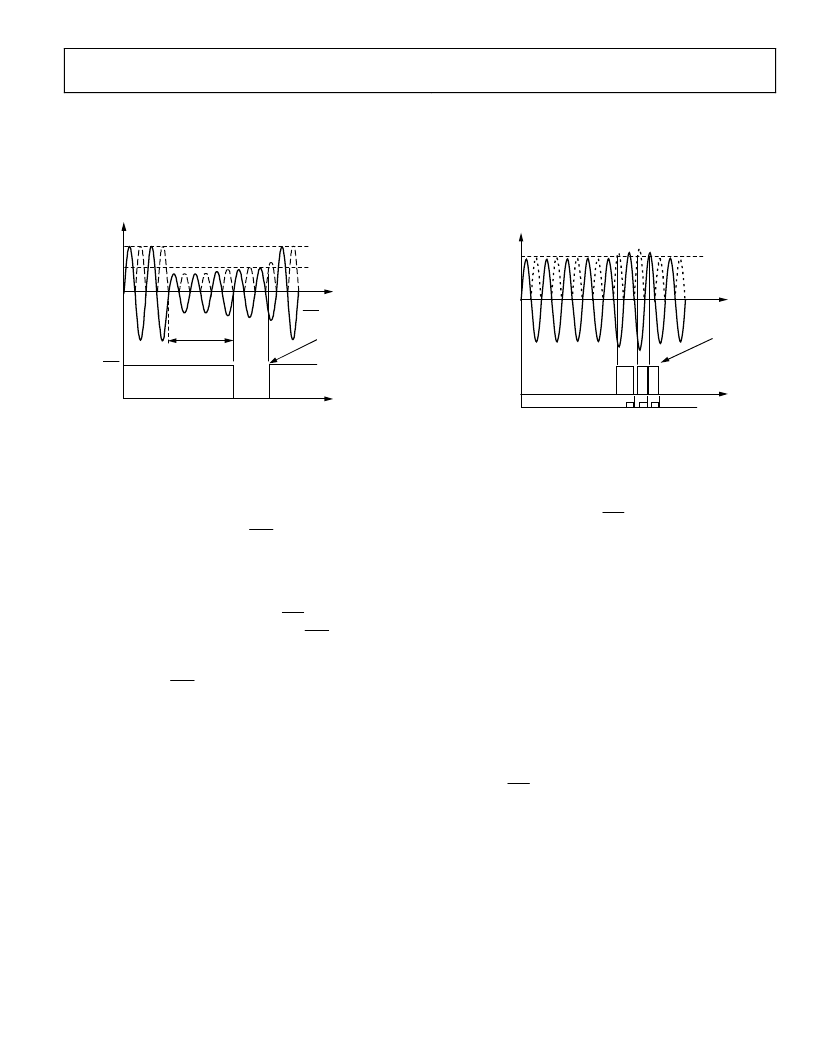

LINE VOLTAGE SAG DETECTION

In addition to detecting the loss of the line voltage when there

are no zero crossings on the voltage channel, the ADE7763 can

also be programmed to detect when the absolute value of the line

voltage drops below a peak value for a specified number of line

cycles. This condition is illustrated in Figure 35.

Rev. A | Page 17 of 56

SAGCYC[7:0] = 0x04

3 LINE CYCLES

SAG RESET HIGH

WHEN CHANNEL 2

EXCEEDS SAGLVL[7:0]

FULL SCALE

SAGLVL[7:0]

SAG

CHANNEL 2

0

Figure 35. Sag Detection

In Figure 35 the line voltage falls below a threshold that

has been set in the sag level register (SAGLVL[7:0]) for three

line cycles. The quantities 0 and 1 are not valid for the SAGCYC

register, and the contents represent one more than the desired

number of full line cycles. For example, if the DISSAG bit in the

mode register is Logic 0 and the sag cycle register

(SAGCYC[7:0]) contains 0x04, the SAG pin goes active low at

the end of the third line cycle for which the line voltage

(Channel 2 signal) falls below the threshold. As is the case when

zero crossings are no longer detected, the sag event is also

recorded by setting the SAG flag in the interrupt status register.

If the SAG enable bit is set to Logic 1, the IRQ logic output will

go active low—see the Interrupts section. The SAG pin goes

logic high again when the absolute value of the signal on Channel

2 exceeds the level set in the sag level register. This is shown in

Figure 35 when the SAG pin goes high again during the fifth line

cycle from the time when the signal on Channel 2 first dropped

below the threshold level.

Sag Level Set

The contents of the sag level register (1 byte) are compared to

the absolute value of the most significant byte output from

LPF1 after it is shifted left by one bit. For example, the nominal

maximum code from LPF1 with a full-scale signal on Channel 2

is 0x2518—see the Channel 2 Sampling section. Shifting one bit

left gives 0x4A30. Therefore, writing 0x4A to the SAG level

register puts the sag detection level at full scale. Writing 0x00 or

0x01 puts the sag detection level at 0. The SAG level register is

compared to the most significant byte of a waveform sample

after the shift left, and detection occurs when the contents of

the sag level register are greater.

PEAK DETECTION

The ADE7763 can also be programmed to detect when the

absolute value of the voltage or current channel exceeds a

specified peak value. Figure 36 illustrates the behavior of the

peak detection for the voltage channel.

Both Channel 1 and Channel 2 are monitored at the same time.

PKV RESET LOW

WHEN RSTSTATUS

REGISTER IS READ

VPKLVL[7:0]

V

2

READ RSTSTATUS

REGISTER

PKV INTERRUPT

FLAG (BIT 8 OF

STATUS REGISTER)

0

Figure 36. Peak Level Detection

Figure 36 shows a line voltage exceeding a threshold that has

been set in the voltage peak register (VPKLVL[7:0]). The

voltage peak event is recorded by setting the PKV flag in the

interrupt status register. If the PKV enable bit is set to Logic 1 in

the interrupt mask register, the IRQ logic output will go active

low. Similarly, the current peak event is recorded by setting the

PKI flag in the interrupt status register—see the Interrupts

section.

Peak Level Set

The contents of the VPKLVL and IPKLVL registers are

compared to the absolute value of Channel 1 and Channel 2,

respectively, after they are multiplied by 2. For example, the

nominal maximum code from the Channel 1 ADC with a full-

scale signal is 0x2851EC—see the Channel 1 Sampling section.

Multiplying by 2 gives 0x50A3D8. Therefore, writing 0x50 to

the IPKLVL register, for example, puts the Channel 1 peak

detection level at full scale and sets the current peak detection

to its least sensitive value. Writing 0x00 puts the Channel 1

detection level at 0. Peak level detection is done by comparing

the contents of the IPKLVL register to the incoming Channel 1

sample. The IRQ pin indicates that the peak level is exceeded if

the PKI or PKV bits are set in the interrupt enable register

(IRQEN [15:0]) at Address 0x0A.

Peak Level Record

The ADE7763 records the maximum absolute value reached by

Channel 1 and Channel 2 in two different registers—IPEAK

and VPEAK, respectively. VPEAK and IPEAK are 24-bit,

unsigned registers. These registers are updated each time the

absolute value of the waveform sample from the corresponding

channel is above the value stored in the VPEAK or IPEAK

register. The contents of the VPEAK register correspond to two

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADE7763ARSRL | Single-Phase Active and Apparent Energy Metering IC |

| ADG804 | 0.5 ohm CMOS 1.65 V TO 3.6 V 4-Channel Multiplexer |

| ADG804YRM | 0.5 ohm CMOS 1.65 V TO 3.6 V 4-Channel Multiplexer |

| ADG804YRM-REEL | 0.5 ohm CMOS 1.65 V TO 3.6 V 4-Channel Multiplexer |

| ADG804YRM-REEL7 | 0.5 ohm CMOS 1.65 V TO 3.6 V 4-Channel Multiplexer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADE7763ARSRL | 制造商:Analog Devices 功能描述:Energy Measurement 20-Pin SSOP T/R |

| ADE7763ARSZ | 功能描述:IC ENERGY METERING 1PHASE 20SSOP RoHS:是 類別:集成電路 (IC) >> PMIC - 能量測量 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:* |

| ADE7763ARSZ | 制造商:Analog Devices 功能描述:IC, SINGLE PHASE ENERGY METER, SSOP-20 |

| ADE7763ARSZRL | 功能描述:IC ENERGY METERING 1PHASE 20SSOP RoHS:是 類別:集成電路 (IC) >> PMIC - 能量測量 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:* |

| ADE7763ARSZRL | 制造商:Analog Devices 功能描述:IC, SINGLE PHASE ENERGY METER, SSOP-20 |

發(fā)布緊急采購,3分鐘左右您將得到回復。