- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378286 > ADV7183A (Analog Devices, Inc.) Multiformat SDTV Video Decoder PDF資料下載

參數(shù)資料

| 型號(hào): | ADV7183A |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Multiformat SDTV Video Decoder |

| 中文描述: | 標(biāo)清多格式視頻解碼器 |

| 文件頁(yè)數(shù): | 32/104頁(yè) |

| 文件大小: | 894K |

| 代理商: | ADV7183A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)當(dāng)前第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)

ADV7183A

CSFM[2:0] C Shaping Filter Mode (SDP), Address 0x17, [7]

The C shaping filter mode bits allow the user to select from a

range of low-pass filters for the chrominance signal. When

switched in automatic mode, the widest filter is selected based

on the video standard/format and user choice (see settings 000

and 001 in Table 63).

Table 63. CSFM Function

CSFM[2:0]

Description

000*

Autoselect 1.5 MHz bandwidth

001

Autoselect 2.17 MHz bandwidth

010

SH1

011

SH2

100

SH3

101

SH4

110

SH5

111

Wideband Mode

*Default value.

Rev. A | Page 32 of 104

0

–10

–20

–30

–40

–50

–60

0

5

4

3

2

1

6

0

FREQUENCY (MHz)

v740a COMBINED C RESAMPLER

A

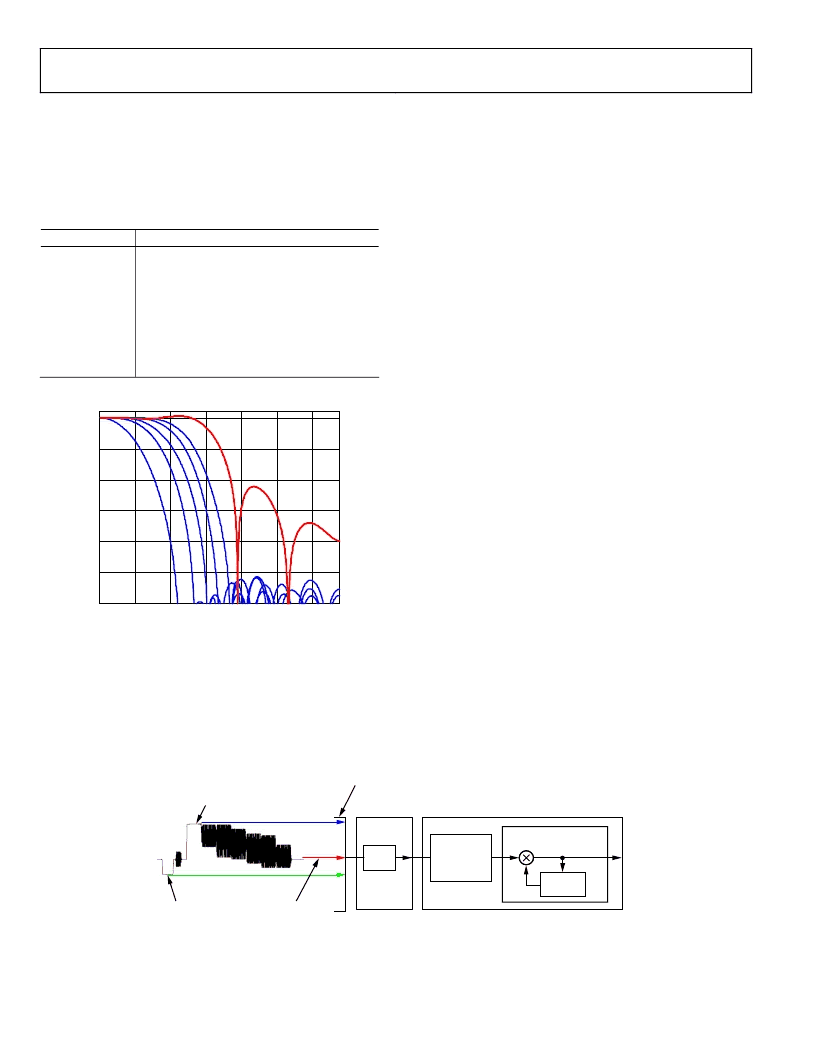

Figure 16. SDP Chroma Shaping Filter Responses

Figure 16 shows the responses of SH1 (narrowest) to SH5

(widest) in addition to the wideband mode (in red).

SDP GAIN OPERATION

The gain control within the ADV7183A is done on a purely

digital basis. The input ADCs support a 10-bit range, mapped

into a 1.6 V analog voltage range. Gain correction takes place

after the digitization in the form of a digital multiplier.

There are several advantages of this architecture over the

commonly used PGA (programmable gain amplifier) before the

ADCs; among them is the fact that the gain is now completely

independent of supply, temperature, and process variations.

As shown in Figure 17, the ADV7183A can decode a video

signal as long as it fits into the ADC window. There are two

components to this: the amplitude of the input signal and the dc

level it resides on. The dc level is set by the clamping circuitry

(see the SDP Clamp Operation section).

If the amplitude of the analog video signal is too high, clipping

may occur, resulting in visual artifacts. The analog input range

of the ADC, together with the clamp level, determines the

maximum supported amplitude of the video signal.

The minimum supported amplitude of the input video is

determined by the SDP core’s ability to retrieve horizontal and

vertical timing and to lock to the color burst (if present).

There are two gain control units, one each for luma and chroma

data. Both can operate independently of each other. The chroma

unit, however, can also take its gain value from the luma path.

Several AGC modes are possible; Table 64 summarizes them.

It is possible to freeze the automatic gain control loops. This will

cause the loops to stop updating and the AGC determined gain

at the time of the freeze stays active until the loop is either

unfrozen or the gain mode of operation is changed.

The currently active gain from any of the modes can be read

back. Please refer to the description of the dual function manual

gain registers, LG[11:0] Luma Gain and CG[11:0] Chroma

Gain, in the SDP Luma Gain and SDP Chroma Gain sections.

0

ANALOG VOLTAGE

RANGE SUPPORTED BY ADC (1.6V RANGE FOR ADV7183A)

DATA

PRE

PROCESSOR

(DPP)

ADC

SDP

(GAIN SELECTION ONLY)

MAXIMUM

VOLTAGE

MINIMUM

VOLTAGE

CLAMP

LEVEL

GAIN

CONTROL

Figure 17. SDP Gain Control Overview

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7183ABST | Multiformat SDTV Video Decoder |

| ADV7183AKST | Multiformat SDTV Video Decoder |

| ADV7330 | Multiformat 11-Bit Triple DAC Video Encoder |

| ADV7330KST | Multiformat 11-Bit Triple DAC Video Encoder |

| ADXL321 | Small and Thin 18 g Accelerometer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7183ABST | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| ADV7183AKST | 制造商:Analog Devices 功能描述:MULTIFORMAT SDTV VIDEO DECODER 制造商:Rochester Electronics LLC 功能描述:10BIT NTSC/PAL/SECAMVIDDECOD I.C - Tape and Reel 制造商:Analog Devices 功能描述:IC VIDEO ENCODER |

| ADV7183AKST-U1 | 制造商:Analog Devices 功能描述:VID DECODER 80LQFP - Bulk |

| ADV7183AKST-X2 | 制造商:Analog Devices 功能描述:VID DECODER - Bulk |

| ADV7183AXST | 制造商:Analog Devices 功能描述:VIDEO DECODER I.C. - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。