- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295111 > AT40KEL040KW1SB (ATMEL CORP) FPGA, 2304 CLBS, 50000 GATES, PQFP160 PDF資料下載

參數(shù)資料

| 型號(hào): | AT40KEL040KW1SB |

| 廠商: | ATMEL CORP |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 2304 CLBS, 50000 GATES, PQFP160 |

| 封裝: | MQFP-160 |

| 文件頁(yè)數(shù): | 42/42頁(yè) |

| 文件大?。?/td> | 670K |

| 代理商: | AT40KEL040KW1SB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)當(dāng)前第42頁(yè)

9

AT40KEL040

4155G–AERO–05/05

The Cell

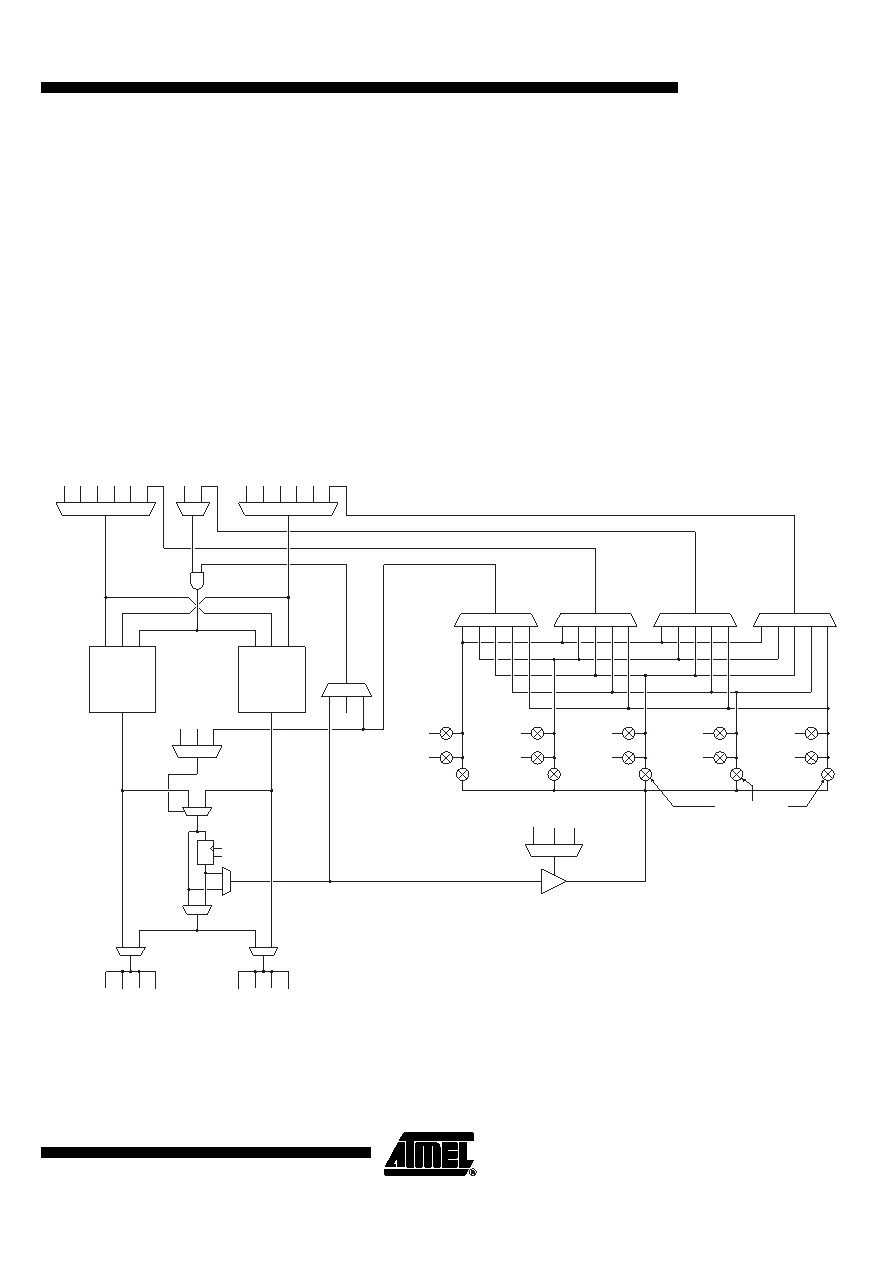

Figure 5 depicts the AT40KEL040 cell. Configuration bits for separate muxes and pass

gates are independent. All permutations of programmable muxes and pass gates are

legal. Vn (V1 -V5) is connected to the vertical local bus in plane n. Hn (H1 -H5) is con-

nected to the horizontal local bus in plane n. A local/local turn in plane n is achieved by

turning on the two pass gates connected to V

n and Hn. Pass gates are opened to let sig-

nals into the cell from a local bus or to drive a signal out onto a local bus. Signals coming

into the logic cell on one local bus plane can be switched onto another plane by opening

two of the pass gates. This allows bus signals to switch planes to achieve greater

routability. Up to five simultaneous local/local turns are possible.

The AT40KEL040 FPGA core cell is a highly configurable logic block based around two

3-input LUTs (8 x 1 ROM), which can be combined to produce one 4-input LUT. This

means that any core cell can implement two functions of 3 inputs or one function of 4

inputs. There is a Set/Reset D flip-flop in every cell, the output of which may be tri-stated

and fed back internally within the core cell. There is also a 2-to-1 multiplexer in every

cell, and an upstream AND gate in the “front end” of the cell. This AND gate is an impor-

tant feature in the implementation of efficient array multipliers.

Figure 5. The Cell

With this functionality in each core cell, the core cell can be configured in several

“modes”. The core cell flexibility makes the AT40KEL040 architecture well suited to

most digital design application areas (see Figure 6).

OUT

RESET/SET

CLOCK

FB

10

Z

D

Q

"1" NW NE SE SW

"1"

"0"

XW

Y

X

ZW

Y

"1"

N

E

S

W

8X1 LUT

X

Y

NW NE SE SW

N

E

S

W

V1

H1

V2

H2

V3

H3

V4

H4

V5

H5

"1" OEH OEV

L

Pass gates

X = Diagonal Direct connect or Bus

Y = Orthogonal Direct Connector Bus

W = Bus Connection

Z = Bus Connection

FB = Internal Feed back

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AT40KEL040KZ1SB | FPGA, 2304 CLBS, 50000 GATES, PQFP256 |

| AT89C2051-12SCT/R | 8-BIT, FLASH, 12 MHz, MICROCONTROLLER, PDSO20 |

| AT89C51-24JCT/R | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PQCC44 |

| AT89C55-12JA | 8-BIT, FLASH, 12 MHz, MICROCONTROLLER, PQCC44 |

| AT90-1263TR | 0 MHz - 3000 MHz RF/MICROWAVE VARIABLE ATTENUATOR, 3.8 dB INSERTION LOSS-MAX |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AT40KEL040KZ1-E | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Rad Hard Reprogrammable FPGAs with FreeRAM |

| AT40K-FFT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:AT40K-FFT [Updated 8/98. 8 Pages] Fast fourier transform Intellectual Property Core for AT40K FPGAs |

| AT40KFL040 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Rad Hard Reprogrammable FPGAs with FreeRAM |

| AT40KFL040KW1-E | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Rad Hard Reprogrammable FPGAs with FreeRAM |

| AT40KFL040KW1-SCC | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Rad Hard Reprogrammable FPGAs with FreeRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。