- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366891 > CR16HCT9VJE8 Microcontroller PDF資料下載

參數(shù)資料

| 型號: | CR16HCT9VJE8 |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件頁數(shù): | 154/157頁 |

| 文件大小: | 1256K |

| 代理商: | CR16HCT9VJE8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁當(dāng)前第154頁第155頁第156頁第157頁

www.national.com

154

When a frame was successfully sent by CR16CAN the con-

tents of the Time Stamp counter are captured into the Time

Stamp register (TSTP) of the transmit buffer during the ACK-

slot of the frame currently being sent. Also, when a message

is received, the TSTP-register of the receiving buffer is load-

ed with the Time Stamp counter value during the ACK-slot of

the CAN frame currently being received.

This means, in the case where a message is received in one

buffer, which was sent from another buffer of the same

CR16CAN node, the TSTP-register contents are equal after

this transaction.

A comparison of the two TSTP-register values can be insert-

ed into a "read from CAN receive buffer" software routine, to

distinguish whether the data received are from another CAN

node (valid) or from the same CAN node (invalid).

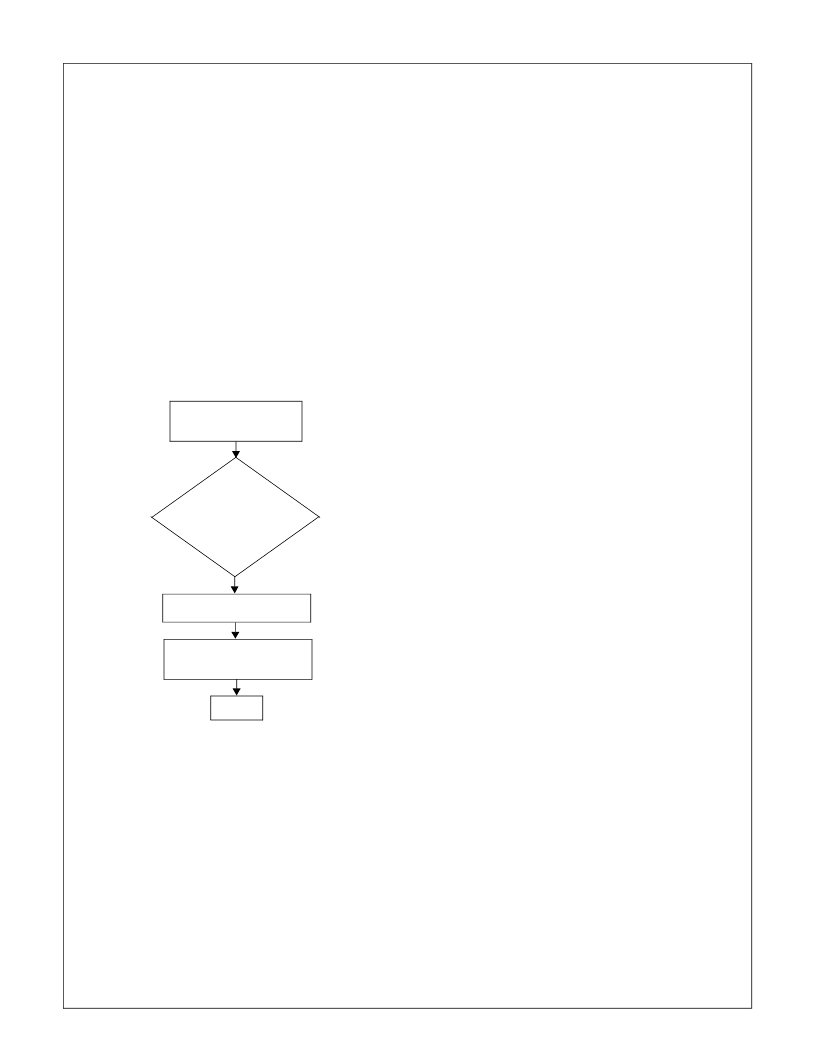

The flowchart below shows a possible implementation. The

same CAN buffer settings as described in Section also apply

to this example.

Modified CAN Receive Sequence:

Advantage:

None of the CAN receive buffers must be disabled at any

time.

Disadvantage:

The receive buffer contents are overwritten by an invalid

message sent from the same CR16CAN node.

26.2

8/16-BIT MICROWIRE/SPI (MWSPI16)

26.2.1

According to the specification, the MSKn clock output in mas-

ter mode should have the value of the MnIDL bit of the

MWnCTL register, even when the module is disabled. How-

ever, the MSKn pin is enabled and the module is disabled.

thus, even if the MnIDL bit is set, the MSKn clock will change

MWSPI16 Problem Description

to a low level as soon as the module is disabled. If any slave

is selected at this time, i will interpret this unwanted transition

as a shift clock.

26.2.2

Even if the module is disabled and the alternate function of

the MSKn pin is enabled, the module can still influence the

MSKn pin and drives the default value ‘0’.

MWSPI16 Problem Cause

26.2.3

When the MSKn idle level of ‘1’ is to be used, the following

procedure should be followed when the module is disabled:

1. Set the MSKn pin to high level in the corresponding port

data output register.

2. Configure the MSKn pin to an output in the correspond-

ing port direction register.

3. Disable the alternate function of the MSKn pin in the cor-

responding port alternate function register.

4. Disable the MWSPI16 module.

MWSPI16 Problem Solutions

26.3

TIMING AND WATCHDOG MODULE

26.3.1

Timing and WATCHDOG Module Problem

Description

The available window for a valid WATCHDOG service varies

with the TWM configuration and the operating mode of the

R16MCS9. Therefore it is not possible to generally provide

the limits for the maximum service window. However, the lim-

its for the minimum service window is guaranteed and should

be used.

26.3.2

Timing and WATCHDOG Module Problem

Cause

The timing and WATCHDOG module uses two different clock

signals for its operation, the slow system clock as well as the

fast system clock.

The slow system clock can either be generated by an exter-

nal 32 kHz quartz or it can be derived from the fast system

clock by means of a prescaler counter in the CLK2RES mod-

ules. The TWM can operate off a maximum slow system

clock of 100 kHz. The WATCHDOG counter (down-counter)

is either clocked directly by the slow system (T0IN) or it is

decremented every time the counter T0 underflows

(T0OUT).

The fast system clock is used for accesses to TWM registers,

which build the user interface of the TWM. These user inter-

face registers include all memory-mapped registers of the

TWM.

Every time the user (CR16B core) writes to a TWM configu-

ration register or to the WATCHDOG Service Data Match

register, this “high speed operation” must be synchronized to

the internal TWM logic running at the slow clock rate. This

synchronization process takes a variable number of low

speed clock cycles, depending on the ratio between the low-

speed and the high-speed system clock and the phase shift

between the two clock signals. The more the two frequencies

differ from each other, the longer it takes the synchronization

process.

In other words, write operations to the TWM registers take a

certain number of low-speed clock cycles to show the desired

effects to the TWM logic.

Message received

into Buffer 1

Time Stamp of

Buffer 1

=

Time Stamp of

Buffer 0

Read out Buffer 1 Data

Reset Buffer 1 Status to

RX_READY

Exit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CR16HCT9VJE8Y | Microcontroller |

| CR16HCT9VJE9 | Microcontroller |

| CR16HCT9VJE9Y | Microcontroller |

| CR16MCT5VJE8Y | Microcontroller |

| CR16MCT5VJE9Y | Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CR16HCT9VJE8Y | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| CR16HCT9VJE9 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| CR16HCT9VJE9Y | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| CR16HCT9VJEX | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:CR16MCT9/CR16MCT5/CR16HCT9/CR16HCT5 16-Bit Reprogrammable/ROM Microcontroller |

| CR16HCT9VJEXY | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:CR16MCT9/CR16MCT5/CR16HCT9/CR16HCT5 16-Bit Reprogrammable/ROM Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。