- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄366891 > CR16HCT9VJE8 Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | CR16HCT9VJE8 |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件頁(yè)數(shù): | 36/157頁(yè) |

| 文件大小: | 1256K |

| 代理商: | CR16HCT9VJE8 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)

www.national.com

36

11.0

Power Management

The Power Management Module (PMM) improves the effi-

ciency of the device by changing the operating mode (and

therefore the power consumption) according to the required

level of device activity.

The device can operate in any of four power modes:

— Active

— Power Save

— Idle

— Halt

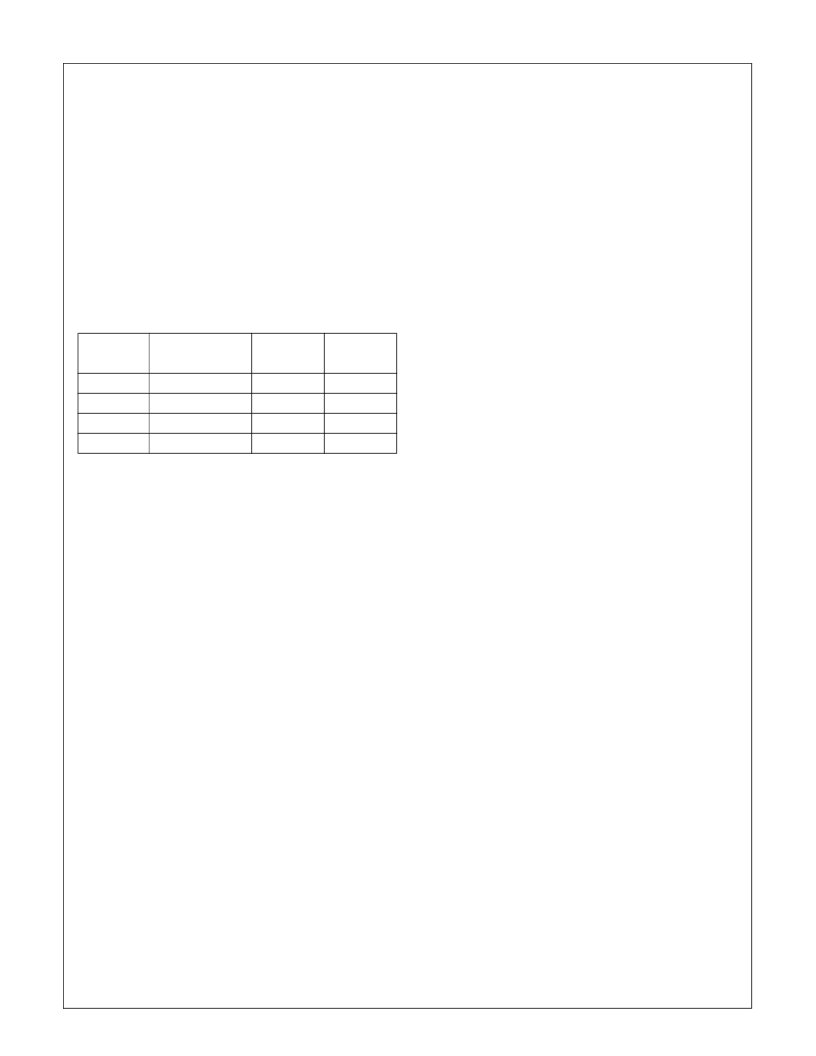

Table 12 summarizes the main properties of the four operat-

ing modes: the state of the high-frequency oscillator (on or

off), the type of clock used by most modules, and the clock

used by the Timing and Watchdog Module (TWM).

Table 12

Power Mode Operating Summary

The low-frequency oscillator continues to operate in all four

modes and power must be provided continuously to the de-

vice power supply pins. In the Halt mode, however, the inter-

nal SLCLK does not toggle, and as a result, the TWM timer

and Watchdog Module do not operate. For the Power Save

and Idle modes, the high-frequency oscillator can be turned

on or off under software control, as long as the low-frequency

oscillator is used.

11.1

In the Active mode, all device modules are fully operational.

This is the operating mode upon reset. Most device modules

use the clock generated by the high-frequency clock oscilla-

tor. The clock rate is determined by the external crystal net-

work.

Power consumption in the Active mode can be reduced by

selectively disabling unused modules and/or by executing

the WAIT instruction. When WAIT is executed, the core stops

executing new instructions and waits for an interrupt.

ACTIVE MODE

11.2

In the Power Save mode, all device modules operate off the

low-frequency clock. If the low-frequency clock is generated

from an external crystal network, the high-frequency clock

oscillator can be turned off to further reduce power consump-

tion.

All on-chip modules continue to operate in the Power Save

mode, with the SLCLK acting as their system clock. If this

mode is entered by using the WAIT command, the CPU is in-

active and waits for an interrupt to wake up. Otherwise, CPU

continues to function normally at the lower frequency of the

slow clock.

The low frequency of the clock in Power Save mode limits the

operation of modules such as the USARTs, MICROWIRE in-

terface, A/D Converter, and timers because they are driven

POWER SAVE MODE

by the slow clock rather than the normal high-speed clock. In

order to work properly in Power Save mode, modules that

perform real-time operations (such as a USART baud rate

generator) must be reprogrammed to use the slower clock.

To reduce power consumption as much as possible, the pro-

gram should execute a WAIT instruction during periods of

CPU inactivity.

11.3

In the Idle mode, the clock is stopped for most of the device.

Only the Power Management Module and Timing and Watch-

dog Module continue to operate. Both of these modules use

the slow clock in this mode.

IDLE MODE

11.4

In the Halt mode, all device clocks are disabled and the high-

frequency oscillator is shut off. In this mode, the device con-

sumes the least possible power while maintaining the device

memory and register contents. The low-frequency oscillator

continues to operate in this mode, but with very low power

consumption due to its power-optimized design.

HALT MODE

11.5

CLOCK INPUTS AND RESET

CONFIGURATION

The system uses a high frequency clock Active mode. The

source of this clock in the device is a high frequency crystal

oscillator. The Oscillating High Frequency Clock (OHFC) in-

put indicates to the Power Management Module (PMM)

when this clock is stable and therefore usable. The clock can

be used when OHFC is set to 1. The PMM does not use the

high frequency clock when OHFC is set to 0. OHFC can be

the output of a clock monitor or a strapped input signal to this

module.

The low frequency clock is used in Power Save mode as the

system clock source. In Idle mode, it is used as the clock

source for the PMM and the TWM, both of which remain

clocked. The clock source may be a low frequency clock os-

cillator or the prescaler from the high frequency clock.

The Oscillating Low Frequency Clock (OLFC) input indicates

to the PMM when the clock is stable and therefore usable.

When OLFC is set to 1, it indicates that the clock can be

used. When OLFC is set to 0, the PMM does not use the low

frequency clock. OLFC is generated by the “slow clock good”

output of the Dual Clock and Reset module (CLK2RES).

While in reset (i.e., the reset signal is active), the PMM out-

puts the clock as long as the clock selected for use upon re-

set is stable (OHFC or OLFC are 1). If the clock selected is

not stable, the PMM clock output remains low.

11.6

Switching from a higher to a lower power consumption mode

is accomplished by writing an appropriate value to the Power

Management Control/Status Register (PMCSR). Switching

from a lower power consumption mode to the Active mode is

usually triggered by a hardware interrupt. Figure 6 shows the

four power consumption modes and the events that trigger a

transition from one mode to another.

Some of the power-up transitions are based on the occur-

rence of a wake-up event. An event of this type can be either

SWITCHING BETWEEN POWER MODES

Mode

High-Frequency

Oscillator

Clock Used TWM Clock

Active

Power Save On or Off

Idle

Halt

On

Main Clock

Slow Clock

None

None

Slow Clock

Slow Clock

Slow Clock

None

On or Off

Off

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CR16HCT9VJE8Y | Microcontroller |

| CR16HCT9VJE9 | Microcontroller |

| CR16HCT9VJE9Y | Microcontroller |

| CR16MCT5VJE8Y | Microcontroller |

| CR16MCT5VJE9Y | Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CR16HCT9VJE8Y | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Microcontroller |

| CR16HCT9VJE9 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Microcontroller |

| CR16HCT9VJE9Y | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Microcontroller |

| CR16HCT9VJEX | 制造商:NSC 制造商全稱(chēng):National Semiconductor 功能描述:CR16MCT9/CR16MCT5/CR16HCT9/CR16HCT5 16-Bit Reprogrammable/ROM Microcontroller |

| CR16HCT9VJEXY | 制造商:NSC 制造商全稱(chēng):National Semiconductor 功能描述:CR16MCT9/CR16MCT5/CR16HCT9/CR16HCT5 16-Bit Reprogrammable/ROM Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。