- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄366891 > CR16MCT5VJE7Y Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | CR16MCT5VJE7Y |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件頁(yè)數(shù): | 12/157頁(yè) |

| 文件大?。?/td> | 1256K |

| 代理商: | CR16MCT5VJE7Y |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)

www.national.com

12

5.0

System Configuration

The device has two input pins, ENV0 and ENV1, which are

used to specify the operating environment of the device upon

reset. There are also two system configuration registers,

called the Module Configuration (MCFG) register and the

Module Status (MSTAT) register.

5.1

Upon reset, the operating mode of the device is determined

by the state of the ENV0 and ENV1 input pins, as indicated

in Table 6.

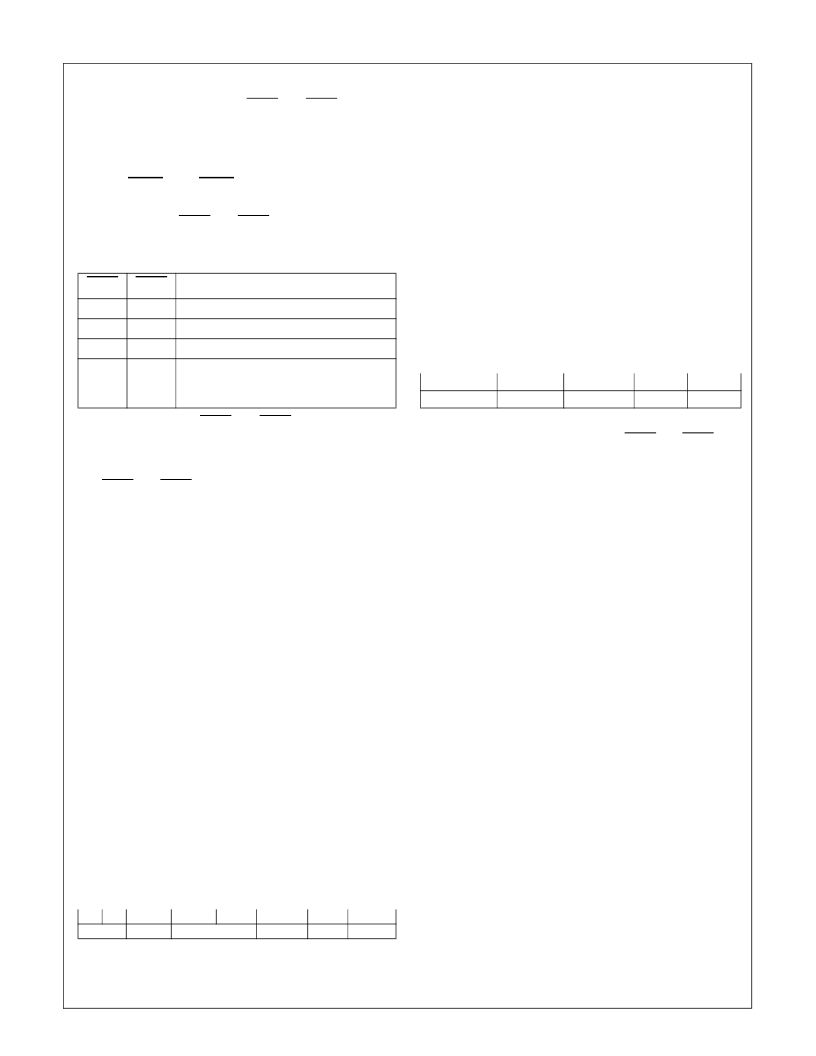

Table 6

Operating Environment Selection

ENV0 AND ENV1 PINS

In the case where the ENV1 and ENV0 pins are both high,

the reset algorithm looks at the FLCTRL2.EMPTY bit to de-

termine whether the program memory is empty, and sets the

operating mode accordingly.

The ENV0 and ENV1 pins have on-chip pull-up devices that

are enabled during reset while the pins are being sampled.

Therefore, if they are left unconnected, the inputs are consid-

ered high and the normal operating mode (IRE-Mode) is se-

lected and the CPU starts to execute code at address 0. To

enter any other operating mode, the external hardware must

drive the appropriate input low.

In the case where the ISP-Mode is selected, the chip starts

executing the ISP code residing in the on-chip ISP-Memory

area.

The test modes are Reserved for factory testing and for ex-

ternal programming of the flash EEPROM program memory.

They should not be invoked otherwise.

5.2

MODULE CONFIGURATION (MCFG)

REGISTER

The MCFG register is a byte-wide, read/write register that

sets the clock output features of the device.

Upon reset, the non-reserved bits of this register are cleared

to zero. The start-up software must write a specific value to

this register in order to configure the CLK output pin function.

When the software writes to this register, it must write a zero

to each reserved bit for the device to operate properly. The

register should be written in active mode only, not in power

save, HALT, or IDLE mode. However, the register contents

are preserved during all power modes.

The MCFG register format is shown below.

CLKOE

CPU Clock Output Enable. When this bit is

cleared (0), the CLK pin (ENV1) remains in the

high-impedance state. When this bit is set (1) in

normal operating mode, the CLK pin operates

as a CPU clock output.

Generated Clock Output 1 Enable. When

cleared (0), the CLKOUT1 pin (ENV0) stays in

high impedance state. When set (1), the pin

outputs the clock from the prescaler controlled

by PRSSC1.SCDIV1.

Generated Clock Output 2 Enable. When this

bit is set (1) and CLKOE is cleared, the

CLKOUT2 pin (ENV1) outputs the clock from

the prescaler controlled by PRSSC1.SCDIV2.

Otherwise, the CLKOUT2 pin is in high imped-

ance state.

CLK1OE

CLK2OE

5.3

The MSTAT register is a byte-wide, read-only register that in-

dicates the general status of the device.

The MCFG register format is shown below.

7

4

3

Reserved

PGMBUSY

Reserved

MODULE STATUS (MSTAT) REGISTER

OENV(1:0)

Operating Environment. These two bits contain

the values applied to the ENV1 and ENV0 pins

upon reset. These bit values are controlled by

the external hardware upon reset and are held

constant in the register until the next reset.

Flash EEPROM Programming Busy. This bit is

automatically set to 1 when either the program

memory or the data memory is busy being pro-

grammed or erased. It is cleared to 0 when nei-

ther of the two flash EEPROM memories is

busy being programmed or erased. When this

bit is set, the software should not attempt any

write access to either of these two memories.

PGMBUSY

ENV1

ENV0

Operating Environment

0

0

1

0

1

0

Test Mode Flash Me3mory

Test Mode

In-System-Programming mode (ISP)

Internal ROM enabled Mode (IRE), if

program memory is not empty; or ISP-

Mode, if program memory is empty

1

1

7

6

5

4

3

2

1

0

Reserved CLK2OE

Reserved

CLK1OE

CLKOE

Reserved

2

1

0

OENV1

OENV0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CR16HCS5VJE8 | Microcontroller |

| CR16HCS9VJE7Y | Microcontroller |

| CR16HCS9VJE8Y | Microcontroller |

| CR16HCT5 | |

| CR16HCT5VJE7Y | Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CR16MCT5VJE8Y | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Microcontroller |

| CR16MCT5VJE9Y | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Microcontroller |

| CR16MCT5VJEXY | 制造商:NSC 制造商全稱(chēng):National Semiconductor 功能描述:CR16MCT9/CR16MCT5/CR16HCT9/CR16HCT5 16-Bit Reprogrammable/ROM Microcontroller |

| CR16MCT9 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述: |

| CR16MCT9VJE7 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。