- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366891 > CR16MCT5VJE7Y Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | CR16MCT5VJE7Y |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件頁數(shù): | 69/157頁 |

| 文件大小: | 1256K |

| 代理商: | CR16MCT5VJE7Y |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁當(dāng)前第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁

69

www.national.com

17.5.2

Upon reset, all non-reserved bits are cleared to 0. The regis-

ter format is shown below.

15 9

8

7

6

5

MCD

V

[6:0]

MICROWIRE Control Register (MWCTL)

MEN

MICROWIRE Enable. This bit enables (1) or

disables (0) the MICROWIRE interface mod-

ule. Clearing this bit disables the module,

clears the status bits in the MICROWIRE status

register (the MBSY, MRBF, and MOVR flags in

MWSTAT), and places the MICROWIRE inter-

face pins in the states described in Table 18.

Table 18

Pin Values with MICROWIRE

Disabled

MMNS

MICROWIRE Master/Slave Select. When

cleared to 0, the device operates as a slave.

When set to 1, the device operates as the mas-

ter.

MICROWIRE Mode Select (8- or 16-bit). When

set to 0, the device operates in 8-bit mode.

When set to 1, the device operates in 16-bit

mode. This bit should only be changed when

MMOD

the module is disabled or the MICROWIRE in-

terface is idle (MWSTAT.MBSY=0).

MICROWIRE Echo Back. This bit enables (1)

or disables (0) the echo back function in slave

mode. This bit should be written only when the

MICROWIRE interface is idle (MWSTAT.MB-

SY=0). The MECH bit is ignored in master

mode. The MWDAT register is valid from the

time the register has been written until the end

of the transfer.

In the echo back mode, MDODI is transmitted

(echoed back) on MDIDO if MWDAT does not

contain any valid data. With the echo back

function disabled, the data held in the MWDAT

register is transmitted on MDIDO, whether or

not the data is valid.

MICROWIRE Enable Interrupt on Overrun.

This bit enables or disables the overrun error

interrupt. When set to 1, an interrupt is gener-

ated when the Receive Overrun Error flag

(MWSTAT.MOVR) is set. Otherwise, no inter-

rupt is generated when an overrun error oc-

curs. This bit should only be enabled in master

mode.

MICROWIRE Enable Interrupt for Read. When

set to 1, an interrupt is generated when the

Read Buffer Full flag (MWSTAT.MRBF) is set.

Otherwise, no interrupt is generated when the

read buffer is full.

MICROWIRE Enable Interrupt for Write. When

set to 1, an interrupt is generated when the

Busy bit (MWSTAT.MBSY) is cleared, which in-

dicates that a data transfer sequence has been

completed and the read buffer is ready to re-

ceive the new data. Otherwise, no interrupt is

generated when the Busy bit is cleared.

MECH

MEIO

MEIR

MEIW

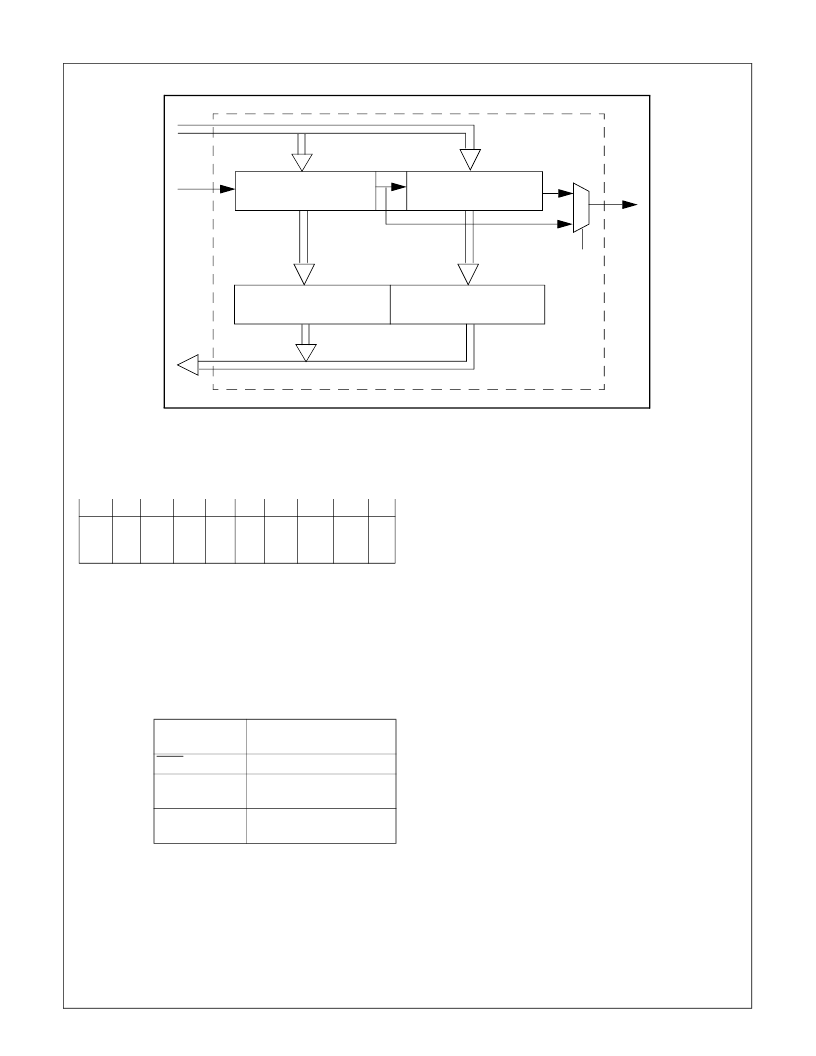

Figure 31.

MWDAT Register Structure

Shift Register

Read Buffer

Low-Byte

High-Byte

write

(store)

1

0

MWMOD

DOUT

DIN

read

(store & MWMOD)

Low-Byte

High-Byte

MWDAT

4

3

2

1

0

MID

L

MSK

M

MEI

W

MEI

R

MEI

O

MEC

H

MMO

D

MMN

S

ME

N

MSK

Master: MnIDL Bit

Slave: input

Input

Master: input

Slave: TRI-STATE

Master: known Value

Slave: input

MCS

MDIDO

MDODI

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CR16HCS5VJE8 | Microcontroller |

| CR16HCS9VJE7Y | Microcontroller |

| CR16HCS9VJE8Y | Microcontroller |

| CR16HCT5 | |

| CR16HCT5VJE7Y | Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CR16MCT5VJE8Y | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| CR16MCT5VJE9Y | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| CR16MCT5VJEXY | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:CR16MCT9/CR16MCT5/CR16HCT9/CR16HCT5 16-Bit Reprogrammable/ROM Microcontroller |

| CR16MCT9 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| CR16MCT9VJE7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。