- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366891 > CR16MCT5VJE7Y Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | CR16MCT5VJE7Y |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件頁數(shù): | 19/157頁 |

| 文件大?。?/td> | 1256K |

| 代理商: | CR16MCT5VJE7Y |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁

19

www.national.com

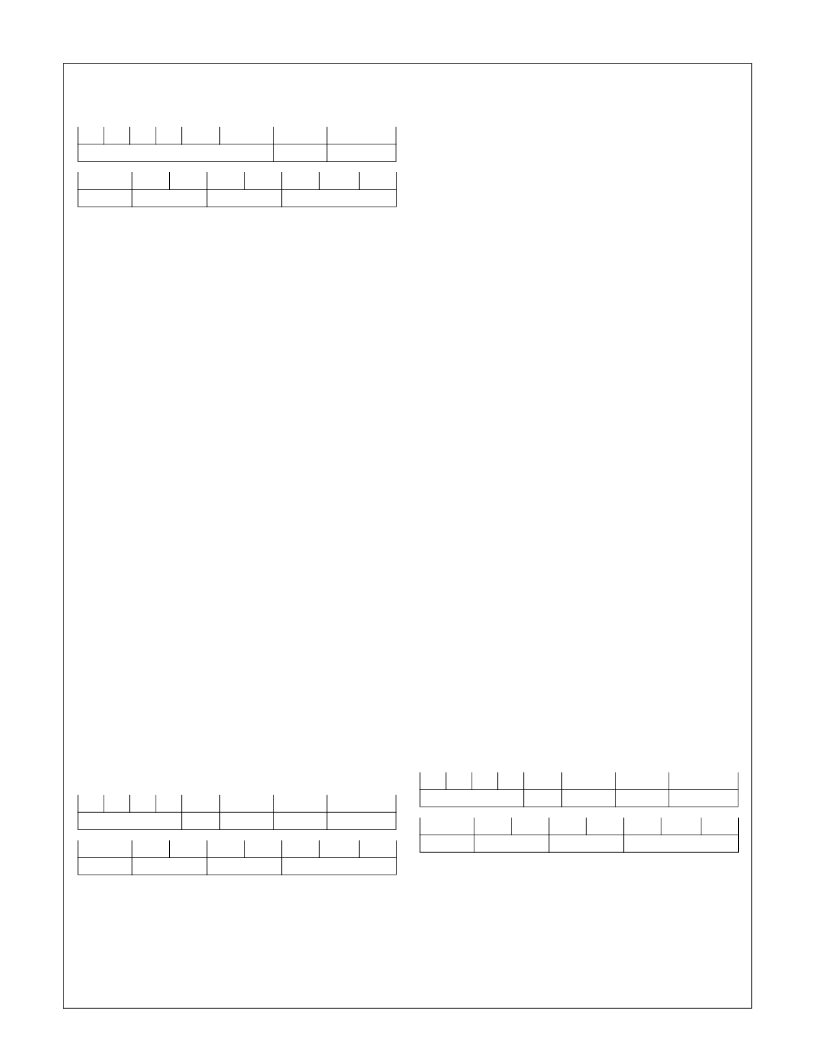

The IOCFG register address is F902 hex. Upon reset, the

register is initialized to 069F hex. The register format is

shown below.

15

14

13

12

11

Reserved

WAIT

Memory Wait cycles

This field specifies the number of TIW (internal

wait state) clock cycles added for each memory

access, ranging from 000 binary for no addi-

tional TIW wait cycles to 111 binary for seven

additional TIW wait cycles.

Memory Hold cycles

This field specifies the number of Thold clock

cycles used for each memory access, ranging

from 00 binary for no Thold cycles to 11 binary

for three Thold clock cycles.

Bus Width.

This bit defines the bus width of the zone.

If cleared to 0, a bus width of 8-bit is used.

if set to 1, a bus width of 16-bit is used.

For the device, a bus width of 16-bit needs to

be set.

Post Idle.

An idle cycle follows the current bus cycle,

when the next bus cycle accesses a different

zone.

If cleared to 0, no idle cycle is inserted.

If set to 1, one idle cycle is inserted.

The IPST bit can be cleared to 0, as no idle cy-

cles are required for on-chip accesses.

Note:

Reserved bits must be cleared to 0 when the CPU

writes to the register.

HOLD

BW

IPST

8.2.3

The Static Zone 0 Configuration (SZCFG0) register is a

word-wide, read/write register that sets the timing and bus

characteristics of Zone 0 memory accesses. In the device im-

plementation of the CompactRISC architecture, Zone 0 is oc-

cupied by the flash EEPROM program memory.

The SCCFG0 register address is F904 hex. Upon reset, the

register is initialized to 069F hex. The register format is

shown below.

15

14

13

12

11

Reserved

FRE

IPRE

Static Zone 0 Configuration (SZCFG0) Register

WAIT

Memory Wait cycles

This field specifies the number of TIW (internal

wait state) clock cycles added for each memory

access, ranging from 000 binary for no addi-

tional TIW wait cycles to 111 binary for seven

additional TIW wait cycles. These bits are ig-

nored if the SZCFG0.FRE bit is set to 1.

HOLD

Memory Hold cycles

This field specifies the number of Thold clock

cycles used for each memory access, ranging

from 00 binary for no Thold cycles to 11 binary

for three Thold clock cycles. These bits are ig-

nored if the SZCFG0.FRE bit is set to 1.

Bus Width.

This bit defines the bus width of the zone.

If cleared to 0, a bus width of 8-bit is used.

if set to 1, a bus width of 16-bit is used.

For the devicedevice a bus width of 16-bit

needs to be set.

Fast Read Enable

This bit enables (1) or disables (0) fast read

bus cycles. A fast read operation takes one

clock cycle. A normal read operation takes at

least two clock cycles.

Post Idle.

An idle cycle follows the current bus cycle,

when the next bus cycle accesses a different

zone.

If cleared to 0, no idle cycle is inserted.

If set to 1, one idle cycle is inserted.

The IPST bit can be cleared to 0, as no idle cy-

cles are required for on-chip accesses.

Preliminary Idle.

An idle cycle is inserted prior to the current bus

cycle, when the new bus cycle accesses a dif-

ferent zone.

If cleared to 0, no idle cycle is inserted.

If set to 1, one idle cycle is inserted.

The IPRE bit can be cleared to 0, as no idle cy-

cles are required for on-chip accesses.

Note:

Reserved bits must be cleared to 0 when the CPU

writes to the register.

BW

FRE

IPST

IPRE

8.2.4

The Static Zone 1 Configuration (SZCFG1) register is a

word-wide, read/write register that sets the timing and bus

characteristics of Zone 1 memory accesses. In the device im-

plementation of the CompactRISC architecture, Zone 1 is oc-

cupied by the boot ROM memory (ISP-Memory).

The SCCFG1 register address is F906 hex. Upon reset, the

register is initialized to 069F hex. The register format is

shown below.

15

14

13

12

11

Reserved

FRE

IPRE

Static Zone 1 Configuration (SZCFG1) Register

WAIT

Memory Wait cycles

This field specifies the number of TIW (internal

wait state) clock cycles added for each memory

access, ranging from 000 binary for no addi-

tional TIW wait cycles to 111 binary for seven

additional TIW wait cycles. These bits are ig-

nored if the SZCFG0.FRE bit is set to 1.

Memory Hold cycles

This field specifies the number of Thold clock

HOLD

10

9

8

IPST

Reserved

7

6

5

4

3

2

1

0

BW

Reserved

HOLD

WAIT

10

9

8

IPST

Reserved

7

6

5

4

3

2

1

0

BW

Reserved

HOLD

WAIT

10

9

8

IPST

Reserved

7

6

5

4

3

2

1

0

BW

Reserved

HOLD

WAIT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CR16HCS5VJE8 | Microcontroller |

| CR16HCS9VJE7Y | Microcontroller |

| CR16HCS9VJE8Y | Microcontroller |

| CR16HCT5 | |

| CR16HCT5VJE7Y | Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CR16MCT5VJE8Y | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| CR16MCT5VJE9Y | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| CR16MCT5VJEXY | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:CR16MCT9/CR16MCT5/CR16HCT9/CR16HCT5 16-Bit Reprogrammable/ROM Microcontroller |

| CR16MCT9 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| CR16MCT9VJE7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。