- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376836 > DP84412N DRAM Controller PDF資料下載

參數(shù)資料

| 型號(hào): | DP84412N |

| 英文描述: | DRAM Controller |

| 中文描述: | DRAM控制器 |

| 文件頁數(shù): | 26/46頁 |

| 文件大小: | 644K |

| 代理商: | DP84412N |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

7.0 Wait Support

(Continued)

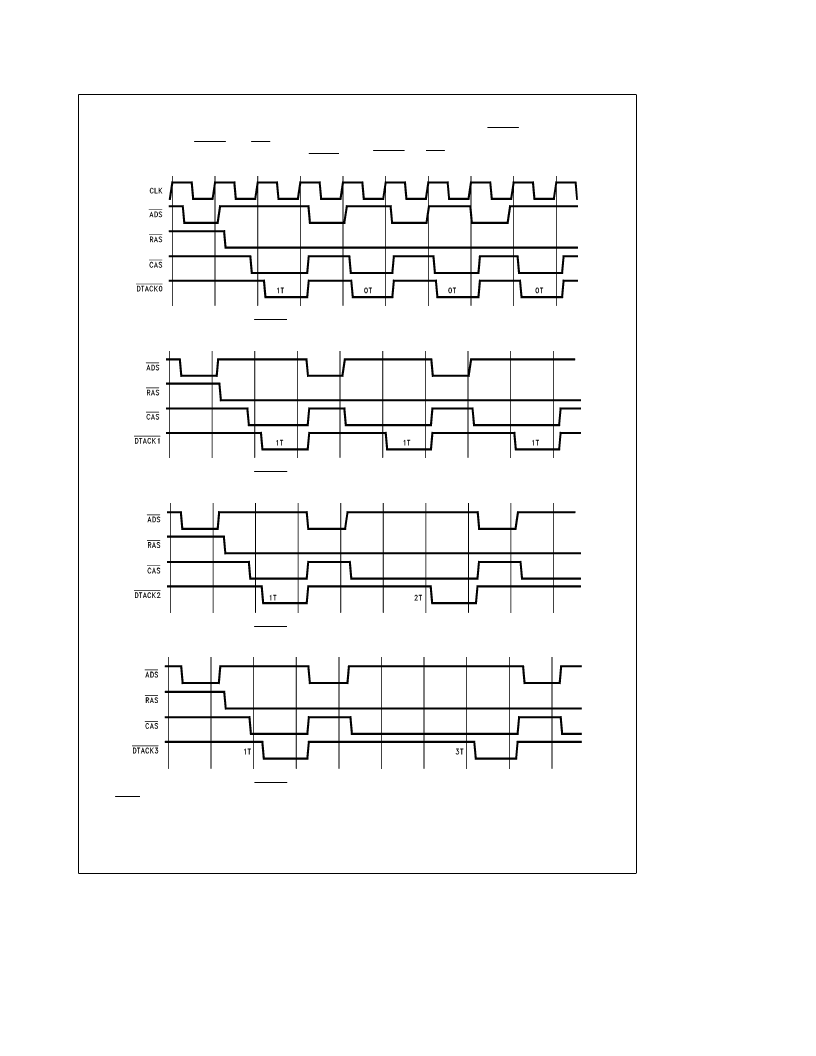

7.2 PAGE ACCESSES

During page accesses, DTACK (and CAS) will assert from

either clock edge according to programming bit ECAS2.

Figure 22 shows different DTACK assertions during page

accesses, they follow an opening access with 1 wait state.

DTACK and CAS assert on the rising edge of clock.

TL/F/11718–16

FIGURE 22a. DTACK is Programmed 1T for Openings and 0T during Page

TL/F/11718–17

FIGURE 22b. DTACK is Programmed 1T for Openings and 1T during Page

TL/F/11718–18

FIGURE 22c. DTACK is Programmed 1T for Openings and 2T during Page

TL/F/11718–19

FIGURE 22d. DTACK is Programmed 1T for Openings and 3T during Page

Note:

DTACK is programmed to assert from a positive clock edge.

26

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DP8441VLJ | DRAM Controller |

| DP84422BN | DRAM Controller |

| DP84422J | DRAM Controller |

| DP84422N | DRAM Controller |

| DP84432J | DRAM Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DP84412N/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

| DP84412N/B+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

| DP8441VLJ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

| DP8441VLJ-25 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:microCMOS Programmable 16/64 Mbit Dynamic RAM Controller/Driver |

| DP8441VLJ-40 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:microCMOS Programmable 16/64 Mbit Dynamic RAM Controller/Driver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。