- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1914 > DS21FF42 (Maxim Integrated Products)IC FRAMER T1 4X4 16CH 300-BGA PDF資料下載

參數(shù)資料

| 型號: | DS21FF42 |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 88/114頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FRAMER T1 4X4 16CH 300-BGA |

| 產(chǎn)品培訓(xùn)模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標(biāo)準(zhǔn)包裝: | 40 |

| 控制器類型: | T1 調(diào)幀器 |

| 接口: | 并行/串行 |

| 電源電壓: | 2.97 V ~ 3.63 V |

| 電流 - 電源: | 300mA |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 300-BBGA |

| 供應(yīng)商設(shè)備封裝: | 300-PBGA(27x27) |

| 包裝: | 管件 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁當(dāng)前第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁

DS21FT42/DS21FF42

75 of 114

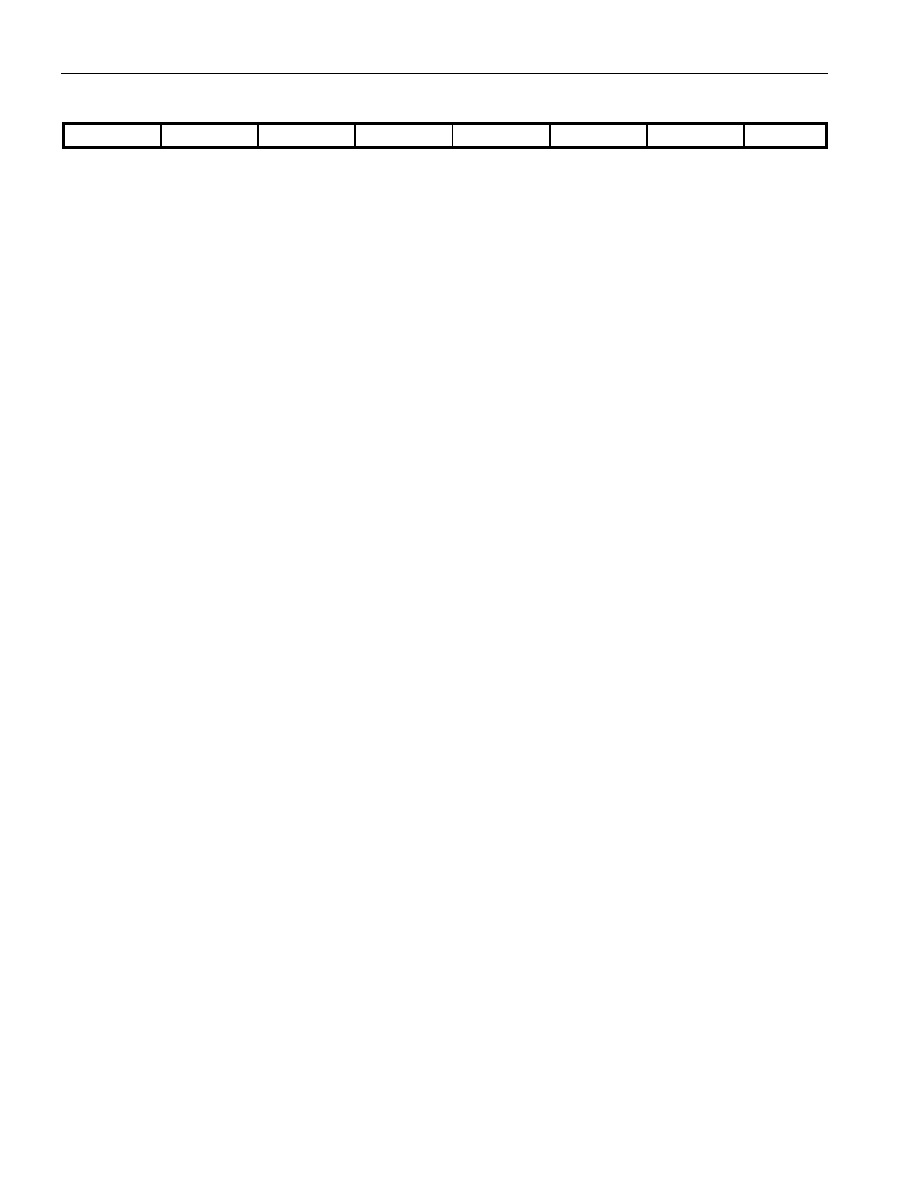

TDC2: TRANSMIT HDLC DS0 CONTROL REGISTER 2 (Address = 93 Hex)

(MSB)

(LSB)

TDB8

TDB7

TDB6

TDB5

TDB4

TDB3

TDB2

TDB1

SYMBOL

POSITION

NAME AND DESCRIPTION

TDB8

TDC2.7

DS0 Bit 8 Suppress Enable. MSB of the DS0. Set to one to

stop this bit from being used.

TDB7

TDC2.6

DS0 Bit 7 Suppress Enable. Set to one to stop this bit from

being used.

TDB6

TDC2.5

DS0 Bit 6 Suppress Enable. Set to one to stop this bit from

being used.

TDB5

TDC2.4

DS0 Bit 5 Suppress Enable. Set to one to stop this bit from

being used.

TDB4

TDC2.3

DS0 Bit 4 Suppress Enable. Set to one to stop this bit from

being used.

TDB3

TDC2.2

DS0 Bit 3 Suppress Enable. Set to one to stop this bit from

being used.

TDB2

TDC2.1

DS0 Bit 2 Suppress Enable. Set to one to stop this bit from

being used.

TDB1

TDC2.0

DS0 Bit 1 Suppress Enable. LSB of the DS0. Set to one to

stop this bit from being used.

19.2 LEGACY FDL SUPPORT

19.2.1 Overview

The DS21Q42 maintains the circuitry that existed in the previous generation of Dallas Semiconductor’s

single chip transceivers and quad framers. Section 19.2 covers the circuitry and operation of this legacy

functionality. In new applications, it is recommended that the HDLC controller and BOC controller

described in Section 19.1 be used. On the receive side, it is possible to have both the new HDLC/BOC

controller and the legacy hardware working at the same time. However this is not possible on the

transmit side since their can be only one source the of the FDL data internal to the device.

19.2.2 Receive Section

In the receive section, the recovered FDL bits or Fs bits are shifted bit–by–bit into the Receive FDL

register (RFDL). Since the RFDL is 8 bits in length, it will fill up every 2 ms (8 times 250 us). The

framer will signal an external microcontroller that the buffer has filled via the SR2.4 bit. If enabled via

IMR2.4, the INT* pin will toggle low indicating that the buffer has filled and needs to be read. The user

has 2 ms to read this data before it is lost. If the byte in the RFDL matches either of the bytes

programmed into the RMTCH1 or RMTCH2 registers, then the SR2.2 bit will be set to a one and the

INT* pin will toggled low if enabled via IMR2.2. This feature allows an external microcontroller to

ignore the FDL or Fs pattern until an important event occurs.

The framer also contains a zero destuffer, which is controlled via the CCR2.0 bit. In both ANSI T1.403

and TR54016, communications on the FDL follows a subset of a LAPD protocol. The LAPD protocol

states that no more than 5 ones should be transmitted in a row so that the data does not resemble an

opening or closing flag (01111110) or an abort signal (11111111). If enabled via CCR2.0, the DS21Q42

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS21FF44 | IC FRAMER E1 4X4 16CH 300-BGA |

| DS21FT44N+ | IC FRAMER 4X4 16CH 300-BGA |

| DS21Q352B | IC TXRX QUAD T1/E1 3.3V 256-BGA |

| DS21Q41BT | IC FRAMER T1 QUAD 128-TQFP |

| DS21Q42T+ | IC FRAMER ENHANCED T1 4X 128TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS21FF42+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 4x4 16/4x3 12 Chnl T1/T1 Framer RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21FF42N | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21FF42N+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 4x4 16/4x3 12 Chnl T1/T1 Framer RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21FF44 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 4x4 16/4x3 12 Chnl E1/E1 Framer RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21FF44N | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。