- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384279 > EDE1104ABSE-6E-E (ELPIDA MEMORY INC) 1G bits DDR2 SDRAM PDF資料下載

參數(shù)資料

| 型號: | EDE1104ABSE-6E-E |

| 廠商: | ELPIDA MEMORY INC |

| 元件分類: | DRAM |

| 英文描述: | 1G bits DDR2 SDRAM |

| 中文描述: | 256M X 4 DDR DRAM, 0.45 ns, PBGA68 |

| 封裝: | ROHS COMPLIANT, FBGA-68 |

| 文件頁數(shù): | 76/82頁 |

| 文件大?。?/td> | 618K |

| 代理商: | EDE1104ABSE-6E-E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁當(dāng)前第76頁第77頁第78頁第79頁第80頁第81頁第82頁

EDE1104ABSE, EDE1108ABSE, EDE1116ABSE

Data Sheet E0852E50 (Ver. 5.0)

76

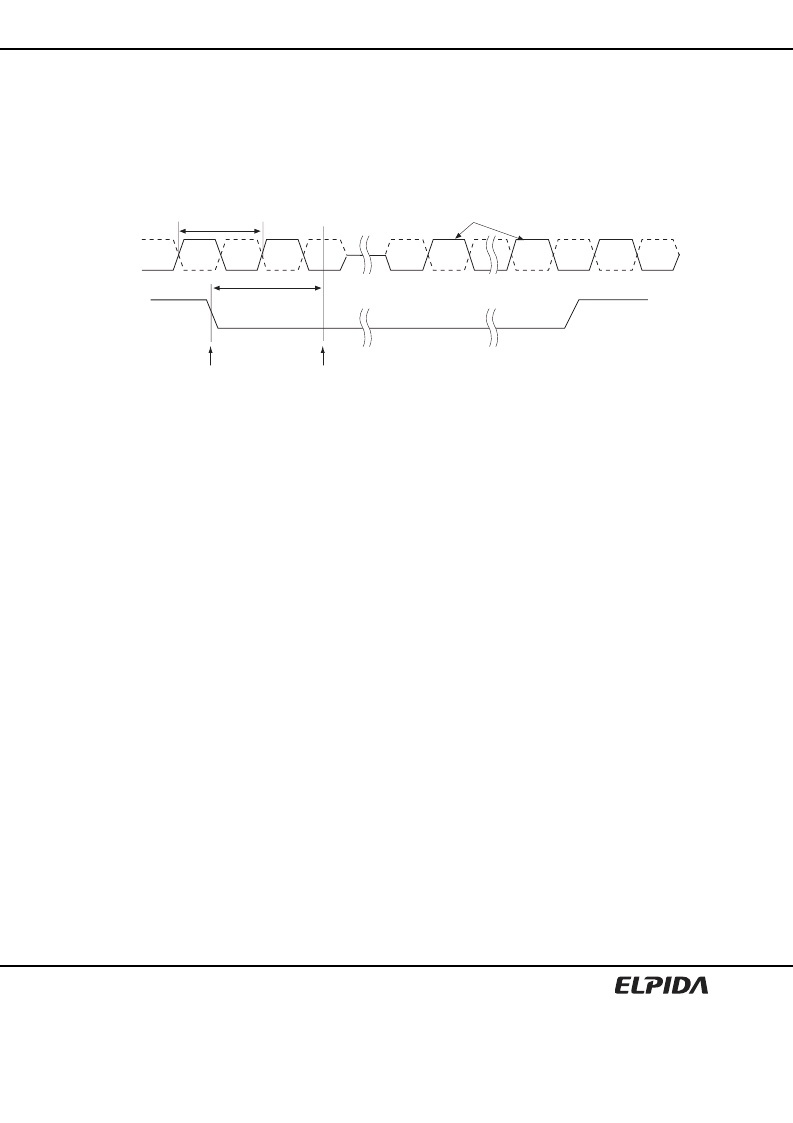

Asynchronous CKE Low Event

DRAM requires CKE to be maintained high for all valid operations as defined in this data sheet. If CKE

asynchronously drops low during any valid operation DRAM is not guaranteed to preserve the contents of array. If

this event occurs, memory controller must satisfy DRAM timing specification tDELAY before turning off the clocks.

Stable clocks must exist at the input of DRAM before CKE is raised high again. DRAM must be fully re-initialized

(steps 4 through 13) as described in initialization sequence. DRAM is ready for normal operation after the

initialization sequence. See AC Characteristics table for tDELAY specification

tCK

CK

/CK

tDELAY

CKE

CKE asynchronously

drops low

Clocks can be

turned off after

this point

Stable clocks

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EDE1104ABSE-8E-E | 1G bits DDR2 SDRAM |

| EDE1108ABSE | 1G bits DDR2 SDRAM |

| EDE1108ABSE-4A-E | 1G bits DDR2 SDRAM |

| EDE1108ABSE-5C-E | 1G bits DDR2 SDRAM |

| EDE1108ABSE-6C-E | 1G bits DDR2 SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EDE1104ABSE-8E-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:1G bits DDR2 SDRAM |

| EDE1104ACBG | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:1G bits DDR2 SDRAM |

| EDE1104ACBG-5C-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:1G bits DDR2 SDRAM |

| EDE1104ACBG-6E-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:1G bits DDR2 SDRAM |

| EDE1104ACBG-8E-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:1G bits DDR2 SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。