- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄1920 > EPM7512BFC256-5 (Altera)IC MAX 7000 CPLD 512 256-FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | EPM7512BFC256-5 |

| 廠商: | Altera |

| 文件頁(yè)數(shù): | 18/66頁(yè) |

| 文件大小: | 0K |

| 描述: | IC MAX 7000 CPLD 512 256-FBGA |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | MAX® 7000B |

| 可編程類(lèi)型: | 系統(tǒng)內(nèi)可編程 |

| 最大延遲時(shí)間 tpd(1): | 5.5ns |

| 電壓電源 - 內(nèi)部: | 2.375 V ~ 2.625 V |

| 邏輯元件/邏輯塊數(shù)目: | 32 |

| 宏單元數(shù): | 512 |

| 門(mén)數(shù): | 10000 |

| 輸入/輸出數(shù): | 212 |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 256-BGA |

| 供應(yīng)商設(shè)備封裝: | 256-FBGA(17x17) |

| 包裝: | 托盤(pán) |

| 其它名稱(chēng): | 544-2361 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)

Altera Corporation

25

MAX 7000B Programmable Logic Device Data Sheet

Programmable Pull-Up Resistor

Each MAX 7000B device I/O pin provides an optional programmable

pull-up resistor during user mode. When this feature is enabled for an I/O

pin, the pull-up resistor (typically 50 k) weakly holds the output to

VCCIO level.

Bus Hold

Each MAX 7000B device I/O pin provides an optional bus-hold feature.

When this feature is enabled for an I/O pin, the bus-hold circuitry weakly

holds the signal at its last driven state. By holding the last driven state of

the pin until the next input signals is present, the bus-hold feature can

eliminate the need to add external pull-up or pull-down resistors to hold

a signal level when the bus is tri-stated. The bus-hold circuitry also pulls

undriven pins away from the input threshold voltage where noise can

cause unintended high-frequency switching. This feature can be selected

individually for each I/O pin. The bus-hold output will drive no higher

than VCCIO to prevent overdriving signals. The propagation delays

through the input and output buffers in MAX 7000B devices are not

affected by whether the bus-hold feature is enabled or disabled.

The bus-hold circuitry weakly pulls the signal level to the last driven state

through a resistor with a nominal resistance (RBH) of approximately

8.5 k. Table 12 gives specific sustaining current that will be driven

through this resistor and overdrive current that will identify the next

driven input level. This information is provided for each VCCIO voltage

level.

The bus-hold circuitry is active only during user operation. At power-up,

the bus-hold circuit initializes its initial hold value as VCC approaches the

recommended operation conditions. When transitioning from ISP to User

Mode with bus hold enabled, the bus-hold circuit captures the value

present on the pin at the end of programming.

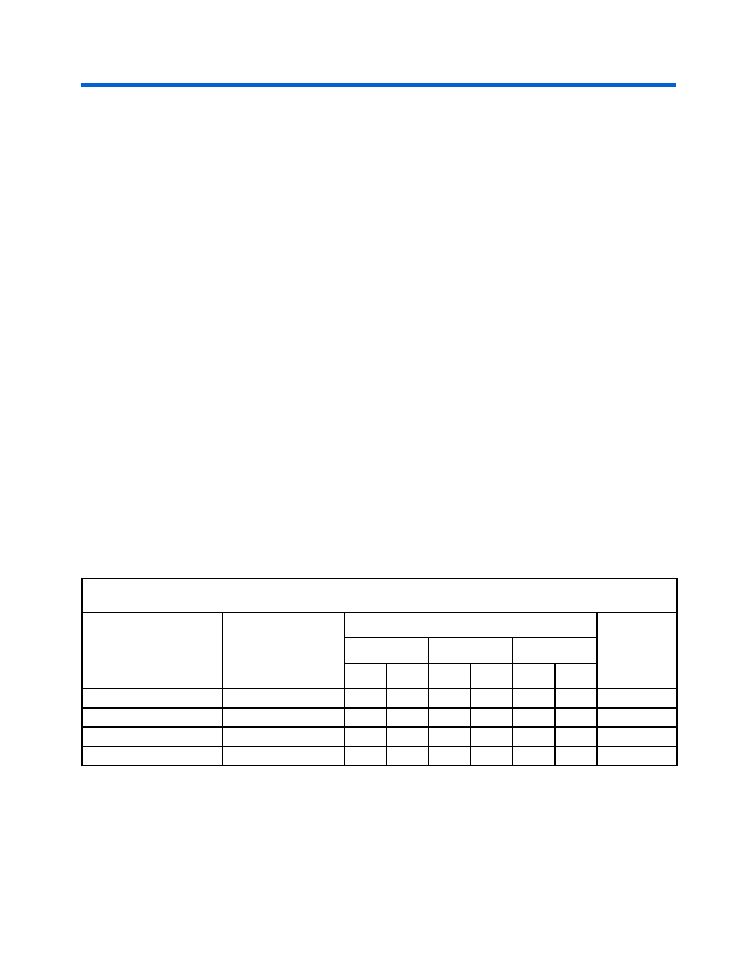

Table 12. Bus Hold Parameters

Parameter

Conditions

VCCIO Level

Units

1.8 V

2.5 V

3.3 V

MinMax

Low sustaining current

VIN > VIL (max)

30

50

70

μA

High sustaining current

VIN < VIH (min)

–30

–50

–70

μA

Low overdrive current

0 V < VIN < VCCIO

200

300

500

μA

High overdrive current

0 V < VIN < VCCIO

–295

–435

–680

μA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EPM9560RI240-20 | IC MAX 9000 CPLD 560 240-RQFP |

| ET80960JT10016 | IC MPU I960JT 3V 100MHZ 132-QFP |

| EX256-PTQG100I | IC FPGA ANTIFUSE 12K 100-TQFP |

| EXPANDIO-USB-FS-DIL-28 | IC I/O EXPANDER USB 21B 28DIP |

| FIN1001M5 | IC DRIVER 3.3V LVDS HS SOT-23 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPM7512BFC256-5N | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 7000 512 Macro 212 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM7512BFC256-7 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 7000 512 Macro 212 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM7512BFC256-7N | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 7000 512 Macro 212 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM7512BFI256-10 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述: |

| EPM7512BFI256-7 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 7000 512 Macro 212 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。