- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16582 > EVAL-AD9832SDZ (Analog Devices Inc)BOARD EVAL FOR AD9832 PDF資料下載

參數(shù)資料

| 型號: | EVAL-AD9832SDZ |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 22/28頁 |

| 文件大?。?/td> | 0K |

| 描述: | BOARD EVAL FOR AD9832 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁

Data Sheet

AD9832

Rev. E | Page 3 of 28

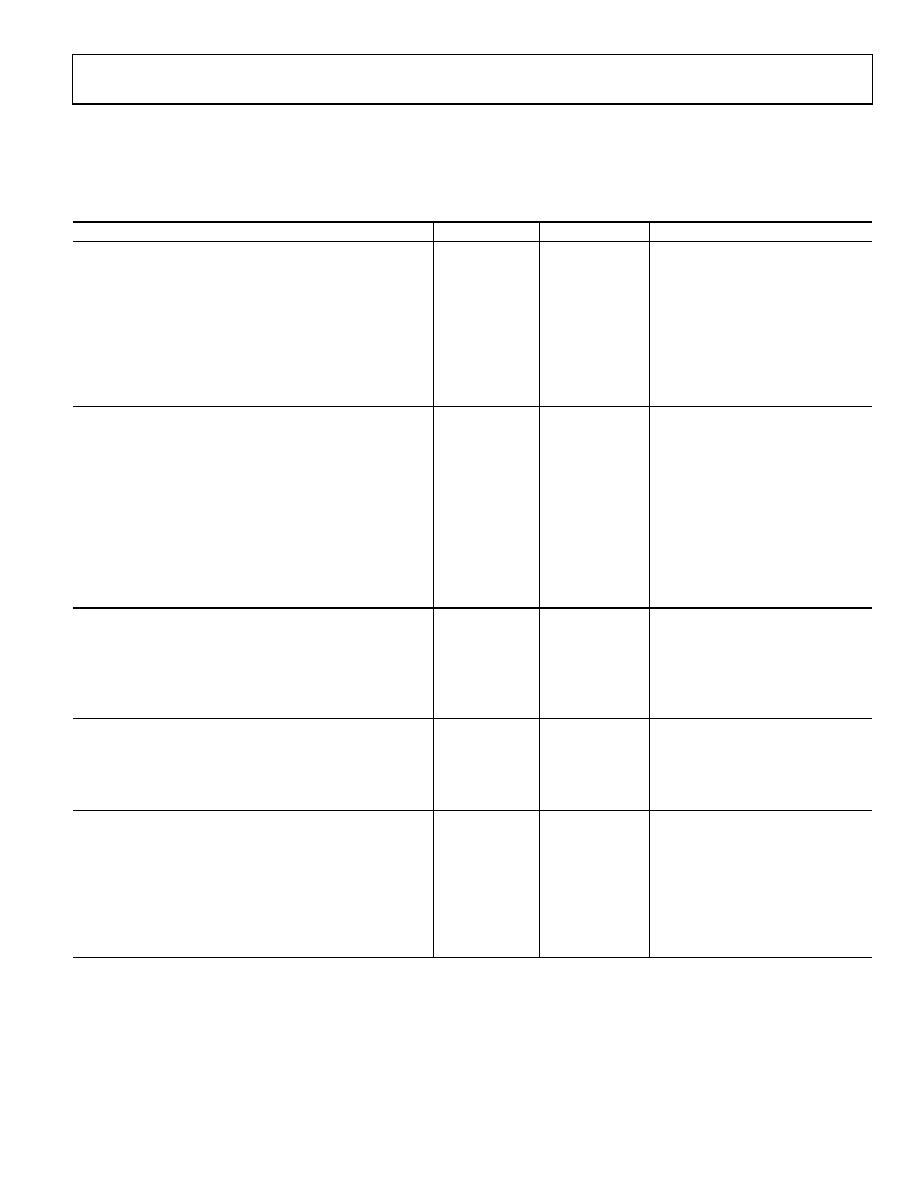

SPECIFICATIONS

VDD = +5 V ± 5%; AGND = DGND = 0 V; TA = TMIN to TMAX; REFIN = REFOUT; RSET = 3.9 k; RLOAD = 300 for IOUT, unless otherwise

noted. Also, see Figure 2.

Table 1.

Parameter1

AD9832B

Unit

Test Conditions/Comments

SIGNAL DAC SPECIFICATIONS

Resolution

10

Bits

Update Rate (fMAX)

25

MSPS nom

IOUT Full Scale

4

mA nom

4.5

mA max

Output Compliance

1.35

V max

3 V power supply

DC Accuracy

Integral Nonlinearity

±1

LSB typ

Differential Nonlinearity

±0.5

LSB typ

DDS SPECIFICATIONS2

Dynamic Specifications

Signal-to-Noise Ratio

50

dB min

fMCLK = 25 MHz, fOUT = 1 MHz

Total Harmonic Distortion

53

dBc max

fMCLK = 25 MHz, fOUT = 1 MHz

Spurious-Free Dynamic Range (SFDR)3

fMCLK = 6.25 MHz, fOUT = 2.11 MHz

Narrow Band (±50 kHz)

72

dBc min

5 V power supply

70

dBc min

3 V power supply

Wideband (±2 MHz)

50

dBc min

Clock Feedthrough

60

dBc typ

Wake-Up Time4

1

ms typ

Power-Down Option

Yes

VOLTAGE REFERENCE

Internal Reference @ 25°C

1.21

V typ

TMIN to TMAX

1.21 ± 7%

V min/V max

REFIN Input Impedance

10

M typ

Reference Temperature Coefficient (TC)

100

ppm/°C typ

REFOUT Output Impedance

300

typ

LOGIC INPUTS

Input High Voltage, VINH

VDD 0.9

V min

Input Low Voltage, VINL

0.9

V max

Input Current, IINH

10

A max

Input Capacitance, CIN

10

pF max

POWER SUPPLIES

AVDD

2.97/5.5

V min/V max

DVDD

2.97/5.5

V min/V max

IAA

5

mA max

5 V power supply

IDD

2.5 + 0.4/MHz

mA typ

5 V power supply

15

mA max

3 V power supply

24

mA max

5 V power supply

Low Power Sleep Mode

350

A max

1

Operating temperature range is 40°C to +85°C.

2

100% production tested.

3

fMCLK = 6.25 MHz, frequency word = 0x5671C71C, and fOUT = 2.11 MHz.

4

See Figure 13. To reduce the wake-up time at low power supplies and low temperature, the use of an external reference is suggested.

5

Measured with the digital inputs static and equal to 0 V or DVDD. The AD9832 is tested with a capacitive load of 50 pF. The part can operate with higher capacitive

loads, but the magnitude of the analog output will be attenuated. For example, a 5 MHz output signal is attenuated by 3 dB when the load capacitance equals 85 pF.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RCM24DRPI | CONN EDGECARD 48POS DIP .156 SLD |

| RBM18DRMS | CONN EDGECARD 36POS .156 WW |

| RMM08DRKN | CONN EDGECARD 16POS DIP .156 SLD |

| CI100505-47NJ | INDUCTOR MULTI LAYER CHIP 47NH |

| RMM08DRKH | CONN EDGECARD 16POS DIP .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EVAL-AD9833EB | 制造商:AD 制造商全稱:Analog Devices 功能描述:+2.5 V to +5.5 V, 25 MHz Low Power CMOS Complete DDS |

| EVAL-AD9833EBZ | 制造商:Analog Devices 功能描述:Evaluation Board For IC Programmable Waveform Generator 制造商:Analog Devices 功能描述:PROGRAMMABLE WAVEFORM GENERATOR - Bulk |

| EVAL-AD9833SDZ | 功能描述:BOARD EVAL FOR AD9833 RoHS:是 類別:編程器,開發(fā)系統(tǒng) >> 評估演示板和套件 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 主要目的:數(shù)字電位器 嵌入式:- 已用 IC / 零件:AD5258 主要屬性:- 次要屬性:- 已供物品:板 相關(guān)產(chǎn)品:AD5258BRMZ1-ND - IC POT DGTL I2C1K 64P 10MSOPAD5258BRMZ10-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ100-ND - IC POT DGTL I2C 100K 64P 10MSOPAD5258BRMZ50-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ1-R7-ND - IC POT DGTL I2C 1K 64P 10MSOPAD5258BRMZ10-R7-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ50-R7-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ100-R7-ND - IC POT DGTL I2C 100K 64P 10MSOP |

| EVAL-AD9834EB | 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk |

| EVAL-AD9834EBZ | 制造商:Analog Devices 功能描述:Evaluation Kit For 20 MW Power, 2.3 V To 5.5 V, 75 MHz Complete DDS 制造商:Analog Devices 功能描述:EVAL KIT FOR 20 MW PWR, 2.3V TO 5.5 V, 75 MHZ COMPLETE DDS - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。