- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370740 > HY5PS12423F 128Mx4|1.8V|8K|D43/D44/D54/D55|DDR II SDRAM - 512M PDF資料下載

參數(shù)資料

| 型號: | HY5PS12423F |

| 英文描述: | 128Mx4|1.8V|8K|D43/D44/D54/D55|DDR II SDRAM - 512M |

| 中文描述: | 128Mx4 | 1.8 | 8K的| D43/D44/D54/D55 |的DDR II內(nèi)存- 512M |

| 文件頁數(shù): | 25/66頁 |

| 文件大?。?/td> | 862K |

| 代理商: | HY5PS12423F |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

Rev. 0.52/Nov. 02 25

HY5PS12423(L)F

HY5PS12823(L)F

HY5PS121623(L)F

BURST LENGTH & TYPE

Read and write accesses to the DDR-II SDRAM are burst oriented, with the burst length being programmable. The

burst length determines the maximum number of column locations that can be accessed for a given Read or Write

command. DDR-II SDRAM supports 4bit burst and 8bit burst modes only. For 8bit burst mode, full interleave address

ordering is supported, however, sequential address ordering is nibble based for ease of implementation.

Accesses within a given burst may be programmed to be either nibble sequential or interleaved; this is referred to as

the burst type and is selected via bit A3. The ordering of accesses within a burst is determined by the burst length, the

burst type and the starting column address, as shown in Burst Definitionon Table

Seamless burst read or write operation are supported. Unlike DDR-I devices, interruption of a burst read or write oper-

ation is prohibited. Therefore the Burst Stop command is not supported on DDR-II SDRAM devices.

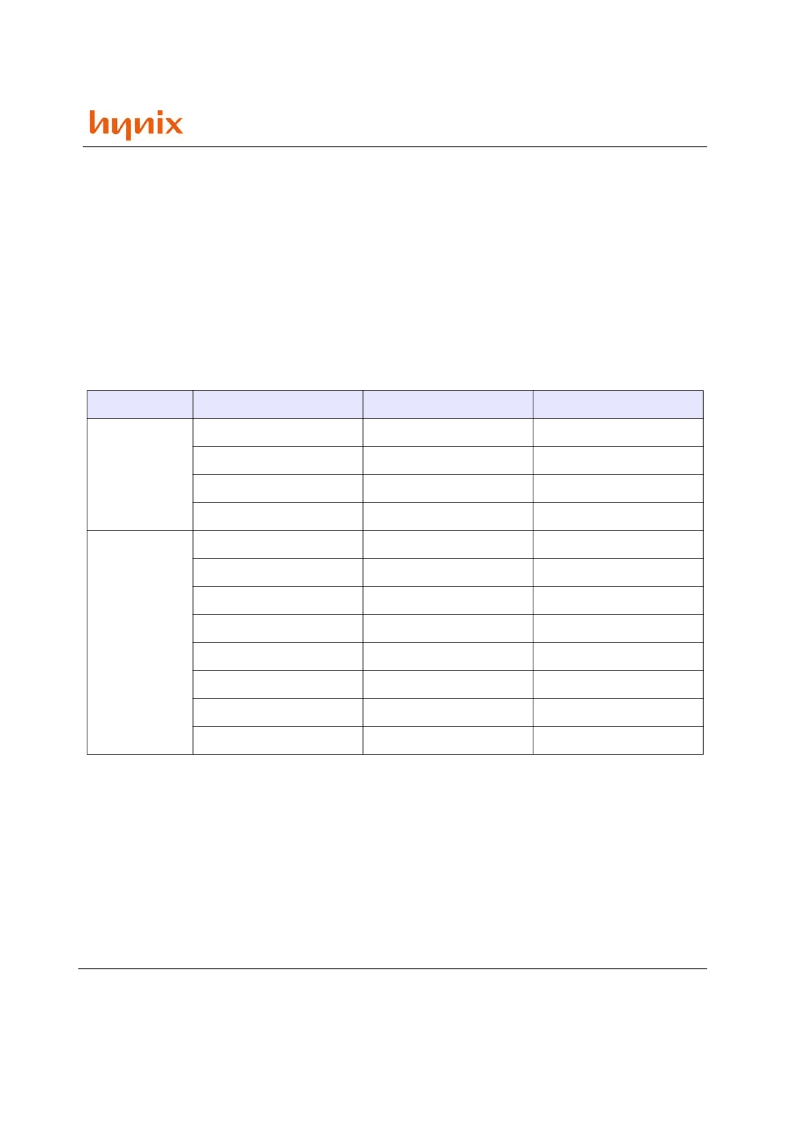

Burst Length and Sequence

Burst Length

Starting Address (A2,A1,A0)

Nibble Sequential

Interleave

4

X00

0, 1, 2, 3

0, 1, 2, 3

X01

1, 2, 3, 0

1, 0, 3, 2

X10

2, 3, 0, 1

2, 3, 0, 1

X11

3, 0, 1, 2

3, 2, 1, 0

8

000

0, 1, 2, 3, 4, 5, 6, 7

0, 1, 2, 3, 4, 5, 6, 7

001

1, 2, 3, 0, 5, 6, 7, 4

1, 0, 3, 2, 5, 4, 7, 6

010

2, 3, 0, 1, 6, 7, 4, 5

2, 3, 0, 1, 6, 7, 4, 5

011

3, 0, 1, 2, 7, 4, 5, 6

3, 2, 1, 0, 7, 6, 5, 4

100

4, 5, 6, 7, 0, 1, 2, 3

4, 5, 6, 7, 0, 1, 2, 3

101

5, 6, 7, 4, 1, 2, 3, 0

5, 4, 7, 6, 1, 0, 3, 2

110

6, 7, 4, 5, 2, 3, 0, 1

6, 7, 4, 5, 2, 3, 0, 1

111

7, 4, 5, 6, 3, 0, 1, 2

7, 6, 5, 4, 3, 2, 1, 0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HY5PS12423LF | 128Mx4|1.8V|8K|D43/D44/D54/D55|DDR II SDRAM - 512M |

| HY5PS12823F | 64Mx8|1.8V|8K|D43/D44/D54/D55|DDR II SDRAM - 512M |

| HY5PS12823LF | 64Mx8|1.8V|8K|D43/D44/D54/D55|DDR II SDRAM - 512M |

| HY5P | Current Transducers HY 5 to 25-P/SP1 |

| HY5R256HC | -|2.5V|8K|40|Direct RDRAM - 256M |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HY5PS12423LF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:128Mx4|1.8V|8K|D43/D44/D54/D55|DDR II SDRAM - 512M |

| HY5PS12821AF | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:512Mb DDR2 SDRAM |

| HY5PS12821AF-C3 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:512Mb DDR2 SDRAM |

| HY5PS12821AF-C4 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:512Mb DDR2 SDRAM |

| HY5PS12821AF-E3 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:512Mb DDR2 SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。