- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10002 > IDT723624L15PF8 (IDT, Integrated Device Technology Inc)IC FIFO SYNC 256X36X2 128QFP PDF資料下載

參數(shù)資料

| 型號(hào): | IDT723624L15PF8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數(shù): | 3/35頁 |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC 256X36X2 128QFP |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 系列: | 7200 |

| 功能: | 同步 |

| 存儲(chǔ)容量: | 18.4K(256 x 36 x 2) |

| 數(shù)據(jù)速率: | 67MHz |

| 訪問時(shí)間: | 15ns |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 128-LQFP |

| 供應(yīng)商設(shè)備封裝: | 128-TQFP(14x20) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 723624L15PF8 |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

11

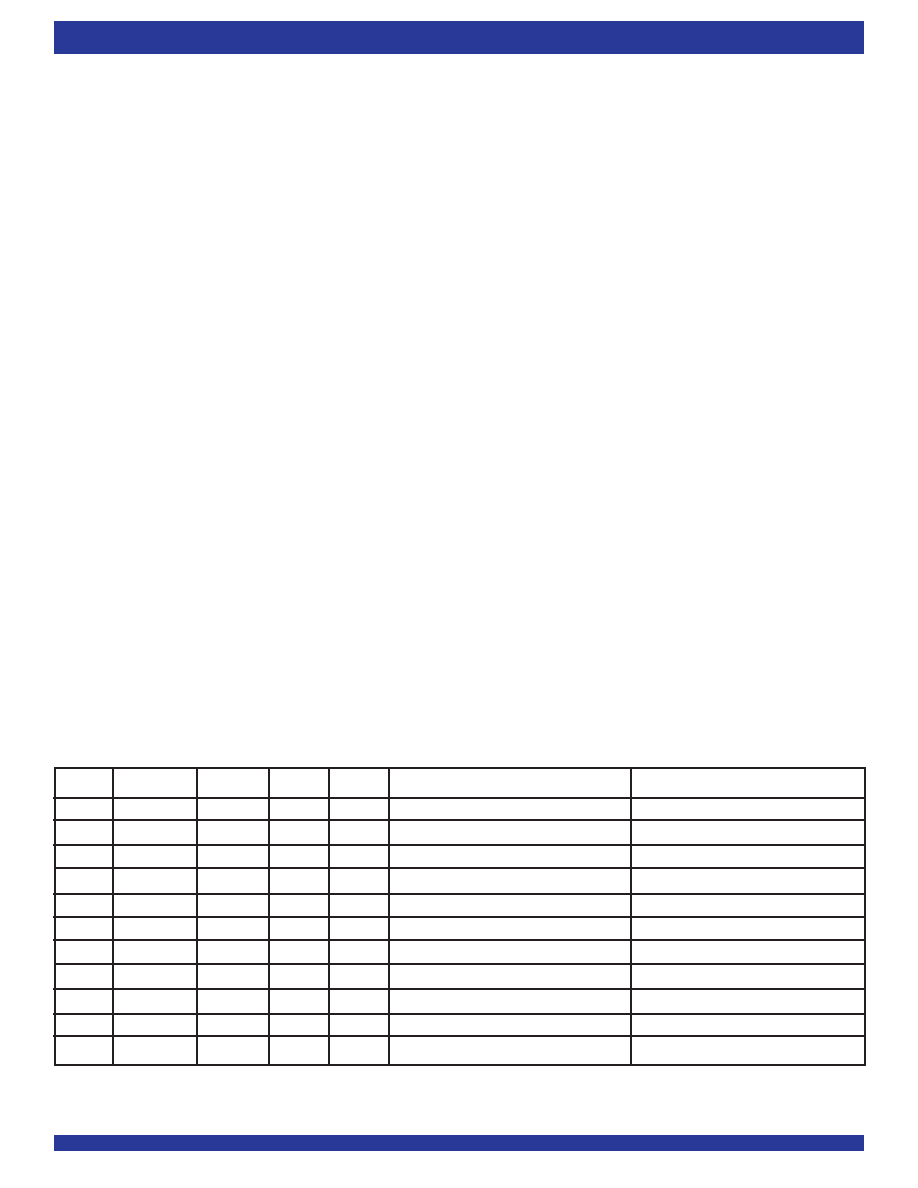

COMMERCIALTEMPERATURERANGE

IDT723624/723634/723644 CMOS SyncBiFIFO WITH BUS-MATCHING

256 x 36 x 2, 512 x 36 x 2, 1,024 x 36 x 2

SPM

FS1/

SEN

FS0/SD

MRS1

MRS2

X1 AND Y1 REGlSTERS(1)

X2 AND Y2 REGlSTERS(2)

HH

H

↑

X64

X

HH

H

↑↑

64

HH

L

↑

X16

X

HH

L

↑↑

16

HL

H

↑

X8

X

HL

H

↑↑

88

HL

L

↑↑

Parallel programming via Port A

LH

L

↑↑

Serial programming via SD

LH

H

↑↑

Reserved

LL

H

↑↑

Reserved

LL

L

↑↑

Reserved

performing a formal read operation. Refer to Figure 3 (Master Reset) for a First

Word Fall Through select timing diagram.

Following Master Reset, the level applied to the BE/

FWFTinputtochoose

the desired timing mode must remain static throughout FIFO operation.

PROGRAMMING THE ALMOST-EMPTY AND ALMOST-FULL FLAGS

FourregistersintheIDT723624/723634/723644areusedtoholdtheoffset

values for the Almost-Empty and Almost-Full flags. The Port B Almost-Empty

flag(

AEB)OffsetregisterislabeledX1andthePortAAlmost-Emptyflag(AEA)

Offset register is labeled X2. The Port A Almost-Full flag (

AFA)Offsetregister

islabeledY1andthePortBAlmost-Fullflag(

AFB)OffsetregisterislabeledY2.

The index of each register name corresponds to its FIFO number. The offset

registers can be loaded with preset values during the reset of a FIFO,

programmed in parallel using the FIFO’s Port A data inputs, or programmed

in serial using the Serial Data (SD) input (see Table 1).

SPM,FS0/SDandFS1/SENfunctionthesamewayinbothIDTStandard

and FWFT modes.

— PRESET VALUES

ToloadaFIFO’sAlmost-EmptyflagandAlmost-FullflagOffsetregisterswith

oneofthethreepresetvalueslistedinTable1,theSerialProgramMode(

SPM)

andatleastoneoftheflag-selectinputsmustbeHIGHduringtheLOW-to-HIGH

transition of its Master Reset input (

MRS1, MRS2). For example, to load the

preset value of 64 into X1 and Y1,

SPM, FS0 and FS1 must be HIGH when

FlFO1reset(

MRS1)returnsHIGH.Flag-offsetregistersassociatedwithFIFO2

are loaded with one of the preset values in the same way with FIFO2 Master

Reset(

MRS2),toggledsimultaneouslywithFIFO1MasterReset(MRS1).For

relevant preset value loading timing diagram, see Figure 3.

— PARALLEL LOAD FROM PORT A

To program the X1, X2, Y1, and Y2 registers from Port A, perform a Master

Reset on both FlFOs simultaneously with

SPMHIGHandFS0andFS1LOW

during the LOW-to-HIGH transition of

MRS1 and MRS2. After this reset is

complete, the first four writes to FIFO1 do not store data in the RAM but load

the offset registers in the order Y1, X1, Y2, X2. The Port A data inputs used by

the offset registers are (A7-A0), (A8-A0), or (A9-A0) for the IDT723624,

IDT723634, or IDT723644, respectively. The highest numbered input is used

asthemostsignificantbitofthebinarynumberineachcase.Validprogramming

values for the registers range from 1 to 252 for the IDT723624; 1 to 508 for the

IDT723634; and 1 to 1,020 for the IDT723644. After all the offset registers are

programmed from Port A, the Port B Full/Input Ready flag (

FFB/IRB) is set

HIGH, and both FIFOs begin normal operation. Refer to Figure 5 for a timing

diagram illustration of parallel programming of the flag offset values.

— SERIAL LOAD

ToprogramtheX1,X2,Y1,andY2registersserially,initiateaMasterReset

with

SPMLOW,FS0/SDLOWandFS1/SENHIGHduringtheLOW-to-HIGH

transitionof

MRS1andMRS2.Afterthisresetiscomplete,theXandYregister

values are loaded bit-wise through the FS0/SD input on each LOW-to-HIGH

transition of CLKA that the FS1/

SEN input is LOW. There are 32-, 36-, or 40-

bitwritesneededtocompletetheprogrammingfortheIDT723624,IDT723634,

or IDT723644, respectively. The four registers are written in the order Y1, X1,

Y2, and finally, X2. The first-bit write stores the most significant bit of the Y1

registerandthelast-bitwritestorestheleastsignificantbitoftheX2register.Each

register value can be programmed from 1 to 508 (IDT723624), 1 to 1,020

(IDT723634), or 1 to 2,044 (IDT723644).

When the option to program the offset registers serially is chosen, the Port

AFull/InputReady(

FFA/IRA)flagremainsLOWuntilallregisterbitsarewritten.

FFA/IRAissetHIGHbytheLOW-to-HIGHtransitionofCLKAafterthelastbit

is loaded to allow normal FIFO1 operation. The Port B Full/Input Ready (

FFB/

IRB) flag also remains LOW throughout the serial programming process, until

allregisterbitsarewritten.

FFB/IRBissetHIGHbytheLOW-to-HIGHtransition

of CLKB after the last bit is loaded to allow normal FIFO2 operation.

See Figure 6 for Serial Programming of the Almost-Full Flag and Almost-

Empty Flag Offset Values (IDT Standard and FWFT Modes).

FIFO WRITE/READ OPERATION

ThestateofthePortAdata(A0-A35)linesiscontrolledbyPortAChipSelect

(

CSA)andPortAWrite/Readselect(W/RA).TheA0-A35linesareintheHigh-

NOTES:

1. X1 register holds the offset for

AEB; Y1 register holds the offset for AFA.

2. X2 register holds the offset for

AEA; Y2 register holds the offset for AFB.

TABLE 1 — FLAG PROGRAMMING

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MS27497T20F16SA | CONN RCPT 16POS WALL MNT W/SCKT |

| LTC2846CG#TR | IC TXRX 3.3V MULTIPROTCOL 36SSOP |

| VI-B4W-MX-B1 | CONVERTER MOD DC/DC 5.5V 75W |

| VE-BNF-MX-B1 | CONVERTER MOD DC/DC 72V 75W |

| LTC2846CG | IC TXRX 3.3V MULTIPROTCOL 36SSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT723624L15PFG | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SYNC 256X36X2 128TQFP |

| IDT723624L15PFG8 | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SYNC 256X36X2 128TQFP |

| IDT723626L12PF | 功能描述:IC FIFO SYNC 256X36X2 128QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT723626L12PF8 | 功能描述:IC FIFO SYNC 256X36X2 128QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT723626L15PF | 功能描述:IC FIFO SYNC 256X36X2 128QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。