- 您現在的位置:買賣IC網 > PDF目錄10002 > IDT723624L15PF8 (IDT, Integrated Device Technology Inc)IC FIFO SYNC 256X36X2 128QFP PDF資料下載

參數資料

| 型號: | IDT723624L15PF8 |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁數: | 4/35頁 |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC 256X36X2 128QFP |

| 標準包裝: | 1,000 |

| 系列: | 7200 |

| 功能: | 同步 |

| 存儲容量: | 18.4K(256 x 36 x 2) |

| 數據速率: | 67MHz |

| 訪問時間: | 15ns |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 128-LQFP |

| 供應商設備封裝: | 128-TQFP(14x20) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | 723624L15PF8 |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

12

COMMERCIALTEMPERATURERANGE

IDT723624/723634/723644 CMOS SyncBiFIFO WITH BUS-MATCHING

256 x 36 x 2, 512 x 36 x 2, 1,024 x 36 x 2

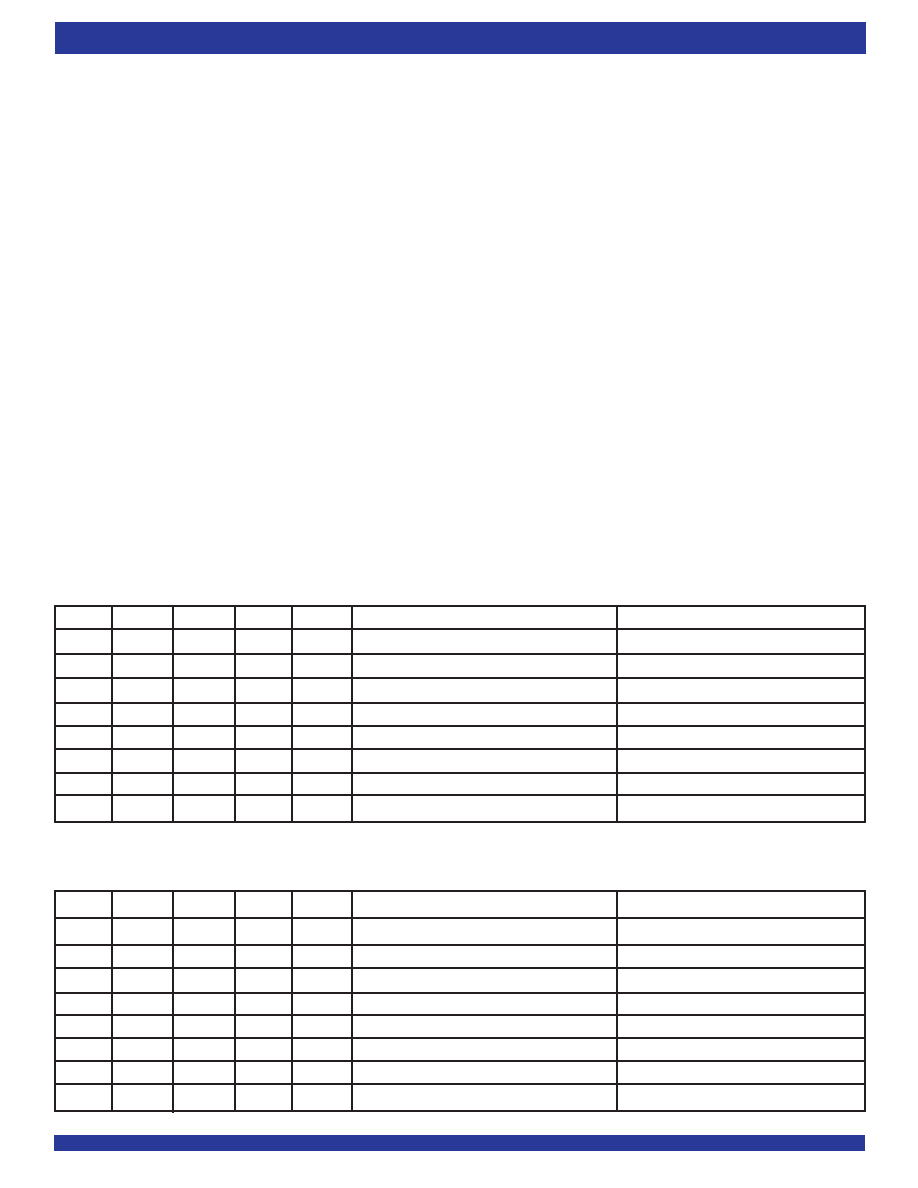

TABLE 2 — PORT A ENABLE FUNCTION TABLE

CSA

W/

RA

ENA

MBA

CLKA

Data A (A0-A35) I/O

PORT FUNCTION

H

X

High-Impedance

None

L

H

L

X

Input

None

LH

H

L

↑

Input

FIFO1 write

LH

H

↑

Input

Mail1 write

L

X

Output

None

LL

H

L

↑

Output

FIFO2 read

L

H

X

Output

None

LL

H

↑

Output

Mail2 read (set

MBF2 HIGH)

CSB

W/RB

ENB

MBB

CLKB

Data B (B0-B35) I/O

PORT FUNCTION

H

X

High-Impedance

None

L

X

Input

None

LL

H

L

↑

Input

FIFO2 write

LL

H

↑

Input

Mail2 write

L

H

L

X

Output

None

LH

H

L

↑

Output

FIFO1 read

L

H

L

H

X

Output

None

LH

H

↑

Output

Mail1 read (set

MBF1 HIGH)

TABLE 3 — PORT B ENABLE FUNCTION TABLE

impedance state when either

CSA or W/RA is HIGH. The A0-A35 lines are

active outputs when both

CSA and W/RA are LOW.

Data is loaded into FIFO1 from the A0-A35 inputs on a LOW-to-HIGH

transition of CLKA when

CSA is LOW, W/RA is HIGH, ENA is HIGH, MBA is

LOW, and

FFA/IRA is HIGH. Data is read from FIFO2 to the A0-A35 outputs

by a LOW-to-HIGH transition of CLKA when

CSAisLOW,W/RAisLOW,ENA

is HIGH, MBA is LOW, and

EFA/ORA is HIGH (see Table 2). FIFO reads and

writes on Port A are independent of any concurrent Port B operation.

The Port B control signals are identical to those of Port A with the exception

thatthePortBWrite/Readselect(

W/RB)istheinverseofthePortAWrite/Read

select (W/

RA). The state of the Port B data (B0-B35) lines is controlled by the

Port B Chip Select (

CSB) and Port B Write/Read select (W/RB). The B0-B35

lines are in the high-impedance state when either

CSB is HIGH or W/RB is

LOW. The B0-B35 lines are active outputs when

CSB is LOW and W/RB is

HIGH.

Data is loaded into FIFO2 from the B0-B35 inputs on a LOW-to-HIGH

transition of CLKB when

CSB is LOW, W/RB is LOW, ENB is HIGH, MBB is

LOW, and

FFB/IRB is HIGH. Data is read from FIFO1 to the B0-B35 outputs

byaLOW-to-HIGHtransitionofCLKBwhen

CSBisLOW,W/RBisHIGH,ENB

is HIGH, MBB is LOW, and

EFB/ORB is HIGH (see Table 3). FIFO reads and

writes on Port B are independent of any concurrent Port A operation.

ThesetupandholdtimeconstraintstotheportclocksfortheportChipSelects

and Write/Read selects are only for enabling write and read operations and

are not related to high-impedance control of the data outputs. If a port enable

is LOW during a clock cycle, the port’s Chip Select and Write/Read select may

change states during the setup and hold time window of the cycle.

WhenoperatingtheFIFOinFWFTmodeandtheOutputReadyflagisLOW,

the next word written is automatically sent to the FIFO’s output register by the

LOW-to-HIGHtransitionoftheportclockthatsetstheOutputReadyflagHIGH.

When the Output Ready flag is HIGH, subsequent data is clocked to the output

registers only when a read is selected using the port’s Chip Select, Write/Read

select, Enable, and Mailbox select.

When operating the FIFO in IDT Standard mode, the first word will cause

the Empty Flag to change state on the second LOW-to-HIGH transition of the

Read clock. The data word will not be automatically sent to the output register.

Instead, data residing in the FIFO’s memory array is clocked to the output

register only when a read is selected using the port’s Chip Select, Write/Read

select, Enable, and Mailbox select. Write and Read timing diagrams for Port

A can be found in Figure 7 and 14. Relevant Port B Write and Read cycle timing

diagrams together with Bus-Matching and Endian select operations can be

found in Figures 8 through 13.

SYNCHRONIZED FIFO FLAGS

Each FIFO is synchronized to its port clock through at least two flip-flop

stages.Thisisdonetoimproveflag-signalreliabilitybyreducingtheprobability

of metastable events when CLKA and CLKB operate asynchronously to one

another.

EFA/ORA, AEA, FFA/IRA, and AFA are synchronized to CLKA.

相關PDF資料 |

PDF描述 |

|---|---|

| MS27497T20F16SA | CONN RCPT 16POS WALL MNT W/SCKT |

| LTC2846CG#TR | IC TXRX 3.3V MULTIPROTCOL 36SSOP |

| VI-B4W-MX-B1 | CONVERTER MOD DC/DC 5.5V 75W |

| VE-BNF-MX-B1 | CONVERTER MOD DC/DC 72V 75W |

| LTC2846CG | IC TXRX 3.3V MULTIPROTCOL 36SSOP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| IDT723624L15PFG | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SYNC 256X36X2 128TQFP |

| IDT723624L15PFG8 | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SYNC 256X36X2 128TQFP |

| IDT723626L12PF | 功能描述:IC FIFO SYNC 256X36X2 128QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標準包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數據速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT723626L12PF8 | 功能描述:IC FIFO SYNC 256X36X2 128QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標準包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數據速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT723626L15PF | 功能描述:IC FIFO SYNC 256X36X2 128QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:7200 標準包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數據速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購,3分鐘左右您將得到回復。