- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377552 > IS43R32400A (Integrated Silicon Solution, Inc.) 4Meg x 32 128-MBIT DDR SDRAM PDF資料下載

參數(shù)資料

| 型號: | IS43R32400A |

| 廠商: | Integrated Silicon Solution, Inc. |

| 英文描述: | 4Meg x 32 128-MBIT DDR SDRAM |

| 中文描述: | 4Meg × 32的128 - Mbit DDR SDRAM內(nèi)存 |

| 文件頁數(shù): | 15/25頁 |

| 文件大?。?/td> | 1295K |

| 代理商: | IS43R32400A |

Integrated Silicon Solution, Inc. — 1-800-379-4774

Rev. 00D

02/15/06

15

ISSI

IS43R32400A

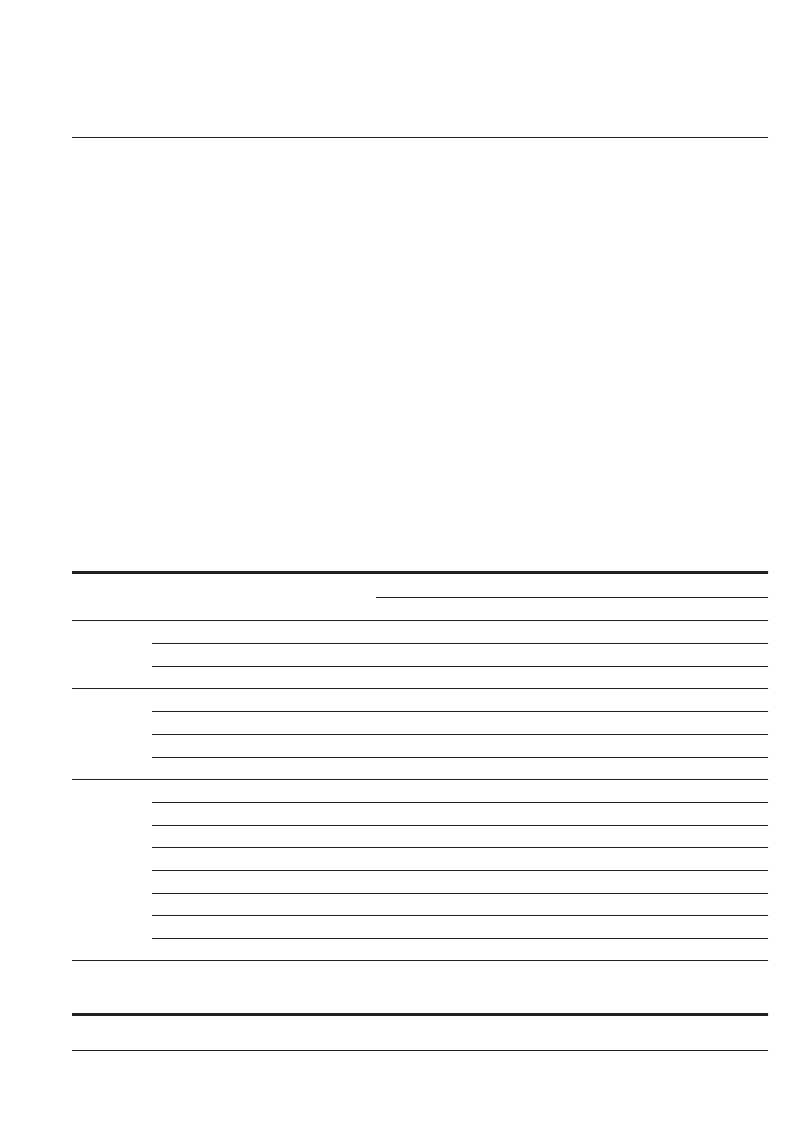

BURST DEFINITION

Burst

Starting Column

Order of Accesses in a Burst

Length

Address

Sequential

Interleaved

A2

A1

A0

2

0

0-1

0-1

1

1-0

1-0

0

0

0-1-2-3

0-1-2-3

4

0

1

1-2-3-0

1-0-3-2

1

0

2-3-0-1

2-3-0-1

1

1

3-0-1-2

3-2-1-0

0

0

0

0-1-2-3-4-5-6-7

0-1-2-3-4-5-6-7

0

0

1

1-2-3-4-5-6-7-0

1-0-3-2-5-4-7-6

0

1

0

2-3-4-5-6-7-0-1

2-3-0-1-6-7-4-5

8

0

1

1

3-4-5-6-7-0-1-2

3-2-1-0-7-6-5-4

1

0

0

4-5-6-7-0-1-2-3

4-5-6-7-0-1-2-3

1

0

1

5-6-7-0-1-2-3-4

5-4-7-6-1-0-3-2

1

1

0

6-7-0-1-2-3-4-5

6-7-4-5-2-3-0-1

1

1

1

7-0-1-2-3-4-5-6

7-6-5-4-3-2-1-0

Full

Page

(up to 256)

Starting

address

n = A0-A7

Cn, Cn + 1, Cn + 2

…Cn - 1,

Cn…

Not Supported

0

BURST LENGTH

The highest access throughput of this device can be

achieved by using a burst of either Read or Write

accesses. The number of accesses in each burst

would be pre-configured to be 2, 4, 8, or full page as

shown in Mode Register Definition (bits M0-M2).

When a Read or Write command is given to the

device, the address bits A0-A7 (x32) select the block

of columns and the starting column for the subsequent

burst. The accesses in this burst can only reference

the selected block, and may wrap-around if a bound-

ary is reached. The Burst Definition table indicates

the relationship between the least significant address

bits and the starting column. The most significant

address bits can select any unique block of columns

in the currently activated row. (Note: Full page bursts

are possible only in Sequential Mode, with the starting

address even.)

BURST TYPE

Bursts can be made in either of two types: sequential

or interleaved. The burst type is programmed during a

Load Mode Register command (bit M3). During a

Read or Write burst, the order of accesses is deter-

mined by burst length, starting column, and burst type,

as indicated in the Burst Definition table.

DLL RESET/CLEAR

To cause a DLL reset, the bit M8 is set to 1 in the

Load Mode Register command. When the DLL is

reset, 200 clock cycles are required to occur prior to

any Read operation. To clear the DLL for normal

operation, the bit M8 is set to 0. This device does not

require it, but JEDEC specifications require that any

time that the DLL is reset, it later be cleared prior for

normal operation.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IS43R32400A-5B | 4Meg x 32 128-MBIT DDR SDRAM |

| IS43R32400A-5BL | 4Meg x 32 128-MBIT DDR SDRAM |

| IS43R32400A-6B | 4Meg x 32 128-MBIT DDR SDRAM |

| IS43R32400A-6BI | 4Meg x 32 128-MBIT DDR SDRAM |

| IS43R32400A-6BL | 4Meg x 32 128-MBIT DDR SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IS43R32400A-5B | 功能描述:動態(tài)隨機存取存儲器 128M 2.5v 4Mx32 400MHz RoHS:否 制造商:ISSI 數(shù)據(jù)總線寬度:16 bit 組織:1 M x 16 封裝 / 箱體:SOJ-42 存儲容量:16 MB 最大時鐘頻率: 訪問時間:50 ns 電源電壓-最大:7 V 電源電壓-最小:- 1 V 最大工作電流:90 mA 最大工作溫度:+ 85 C 封裝:Tube |

| IS43R32400A-5BL | 功能描述:動態(tài)隨機存取存儲器 128M 2.5v 4Mx32 400MHz RoHS:否 制造商:ISSI 數(shù)據(jù)總線寬度:16 bit 組織:1 M x 16 封裝 / 箱體:SOJ-42 存儲容量:16 MB 最大時鐘頻率: 訪問時間:50 ns 電源電壓-最大:7 V 電源電壓-最小:- 1 V 最大工作電流:90 mA 最大工作溫度:+ 85 C 封裝:Tube |

| IS43R32400A-5BL-TR | 功能描述:動態(tài)隨機存取存儲器 128M 2.5v 4Mx32 400MHz RoHS:否 制造商:ISSI 數(shù)據(jù)總線寬度:16 bit 組織:1 M x 16 封裝 / 箱體:SOJ-42 存儲容量:16 MB 最大時鐘頻率: 訪問時間:50 ns 電源電壓-最大:7 V 電源電壓-最小:- 1 V 最大工作電流:90 mA 最大工作溫度:+ 85 C 封裝:Tube |

| IS43R32400A-5B-TR | 功能描述:動態(tài)隨機存取存儲器 128M 2.5v 4Mx32 400MHz RoHS:否 制造商:ISSI 數(shù)據(jù)總線寬度:16 bit 組織:1 M x 16 封裝 / 箱體:SOJ-42 存儲容量:16 MB 最大時鐘頻率: 訪問時間:50 ns 電源電壓-最大:7 V 電源電壓-最小:- 1 V 最大工作電流:90 mA 最大工作溫度:+ 85 C 封裝:Tube |

| IS43R32400A-6B | 功能描述:動態(tài)隨機存取存儲器 128M 2.5v 4Mx32 333MHz RoHS:否 制造商:ISSI 數(shù)據(jù)總線寬度:16 bit 組織:1 M x 16 封裝 / 箱體:SOJ-42 存儲容量:16 MB 最大時鐘頻率: 訪問時間:50 ns 電源電壓-最大:7 V 電源電壓-最小:- 1 V 最大工作電流:90 mA 最大工作溫度:+ 85 C 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。