- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373157 > KM44L32031BT-G(L)0 (SAMSUNG SEMICONDUCTOR CO. LTD.) DDR SDRAM Specification Version 1.0 PDF資料下載

參數(shù)資料

| 型號: | KM44L32031BT-G(L)0 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | DDR SDRAM Specification Version 1.0 |

| 中文描述: | DDR SDRAM的規(guī)范版本1.0 |

| 文件頁數(shù): | 46/53頁 |

| 文件大小: | 669K |

| 代理商: | KM44L32031BT-G(L)0 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁當前第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

- 46 -

REV. 1.0 November. 2. 2000

128Mb DDR SDRAM

9. AC Operating Test Conditions

(V

DD

=2.5V, V

DDQ

=2.5V, T

A

= 0 to 70

°

C)

Parameter

Value

Unit

Note

Input reference voltage for Clock

0.5 * V

DDQ

V

Input signal maximum peak swing

1.5

V

Input signal minimum slew rate

1.0

V/ns

Input Levels(V

IH

/V

IL

)

V

REF

+0.31/V

REF

-0.31

V

Input timing measurement reference level

V

REF

V

Output timing measurement reference level

V

tt

V

Output load condition

See Load Circuit

10. Input/Output Capacitance

(V

DD

=2.5, V

DDQ

=2.5V, T

A

= 25

°

C

,

f=1MHz)

Parameter

Symbol

Min

Max

Delta Cap(max)

Unit

Input capacitance

(A

0

~ A

11

, BA

0

~ BA

1,

CKE, CS, RAS,CAS, WE)

Input capacitance(

CK, CK )

C

IN1

2

3.0

0.5

pF

C

IN2

2

3.0

0.25

pF

Data & DQS input/output capacitance

C

OUT

4.0

5.0

0.5

pF

Input capacitance(DM)

C

IN3

4.0

5.0

pF

Table 15. AC operating test conditions

Table 16. Input/output capacitance

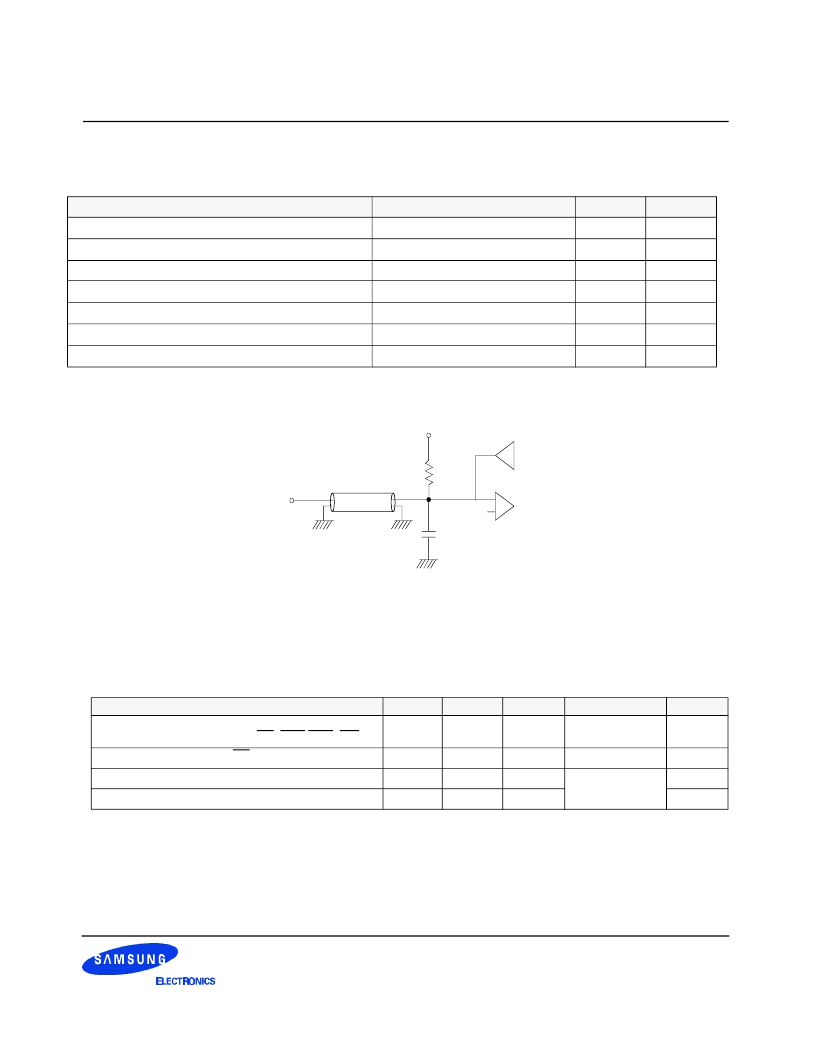

Figure 24. Output Load Circuit (SSTL_2)

Output

Z0=50

C

LOAD

=30pF

V

REF

=0.5*V

DDQ

R

T

=50

V

tt

=0.5*V

DDQ

相關PDF資料 |

PDF描述 |

|---|---|

| KM48L16031BT-G(L)0 | DDR SDRAM Specification Version 1.0 |

| KM416L8031BT-G(L)0 | DDR SDRAM Specification Version 1.0 |

| KM44L32031BT-G(L)Y | DDR SDRAM Specification Version 1.0 |

| KM48S2020C | 1M x 8Bit x 2 Banks Synchronous DRAM(1M x 8位 x 2組同步動態(tài)RAM) |

| KM48S8020B | 4M x 8Bit x 2 Banks Synchronous DRAM(4M x 8位 x 2組同步動態(tài)RAM) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| KM44L32031BT-GLZ/Y/0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR SDRAM Specification Version 1.0 |

| KM44S16020CT-G10 | 制造商:SEC 功能描述: |

| KM44S32030 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:8M x 4Bit x 4 Banks Synchronous DRAM |

| KM44S32030B | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Mbit SDRAM 8M x 4Bit x 4 Banks Synchronous DRAM LVTTL |

| KM44S32030BT-G/F10 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Mbit SDRAM 8M x 4Bit x 4 Banks Synchronous DRAM LVTTL |

發(fā)布緊急采購,3分鐘左右您將得到回復。