- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374388 > KS57C2504 (SAMSUNG SEMICONDUCTOR CO. LTD.) 4-BIT SINGLE-CHIP MICROCONTROLLER FOR SMALL GENERAL-PURPOSE INFRARED REMOTE CONTROL TRANSMITTER PDF資料下載

參數(shù)資料

| 型號: | KS57C2504 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 元件分類: | 4位微控制器 |

| 英文描述: | 4-BIT SINGLE-CHIP MICROCONTROLLER FOR SMALL GENERAL-PURPOSE INFRARED REMOTE CONTROL TRANSMITTER |

| 中文描述: | 4位單片機的小型通用紅外遙控器 |

| 文件頁數(shù): | 26/94頁 |

| 文件大小: | 763K |

| 代理商: | KS57C2504 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁

PRODUCT SPECIFICATION

S3C7254

4–26

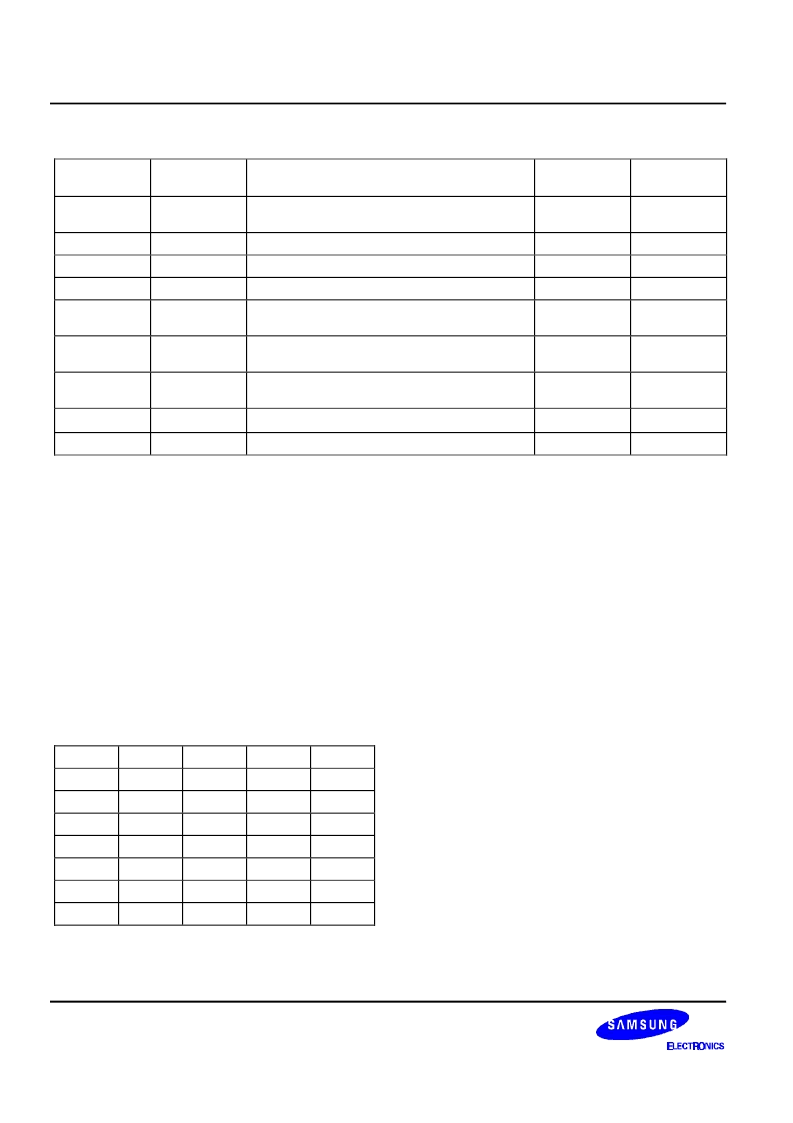

Table 9. Interrupt Request Flag Conditions and Priorities

Interrupt

Source

INTB

Internal /

External

I

Pre-condition for IRQx Flag Setting

Interrupt

Priority

1

IRQ Flag

Name

IRQB

Reference time interval signal from basic

timer

Both rising and falling edges detected at INT4

Rising or falling edge detected at INT0 pin

Rising or falling edge detected at INT1 pin

Completion signal for serial transmit-and-re-

ceive or receive-only operation

Signals for TCNT0 and TREF0 registers

match

When a rising or falling edge detected at any

one of the K0–K3 pins

Rising or falling edge detected at INT2

INT4

INT0

INT1

INTS

E

E

E

I

1

2

3

4

IRQ4

IRQ0

IRQ1

IRQS

INTT0

I

5

IRQT0

INTK

E

6

IRQK

INT2

*

INTW

E

—

IRQ2

I

Time interval of 0.5 second or 3.19 ms

—

IRQW

NOTE

:

The quasi-interrupt INT2 is only used for testing incoming signals.

INTERRUPT ENABLE FLAGS (IEX)

IEx flags, when set to logical one, enable specific

interrupt requests to be serviced. When the interrupt

request flag is set to logical one, an interrupt will not

be serviced until its corresponding IEx flag is also

enabled.

Interrupt enable flags can be read, written, or tested

directly by 1-bit instructions. IEx flags can be

addressed directly at their specific RAM addresses,

despite the current value of the enable memory

bank (EMB) flag.

Table 10. Interrupt Enable and Request Flag

Address

FB8H

FBAH

FBBH

FBCH

FBDH

FBEH

FBFH

Bit 3

IE4

0

0

0

0

IE1

0

Bit 2

IRQ4

0

0

0

0

IRQ1

0

Bit 1

IEB

IEW

IEK

IET0

IES

IE0

IE2

Bit 0

IRQB

IRQW

IRQK

IRQT0

IRQS

IRQ0

IRQ2

NOTES:

1.

2.

IEx refers generically to all interrupt enable flags.

IRQx refers generically to all interrupt request flags.

3.

4.

IEx = 0 is interrupt disable mode.

IEx = 1 is interrupt enable mode.

INTERRUPT PRIORITY REGISTER (IPR)

The 4-bit interrupt priority register (IPR) is used to

control multi-level interrupt handling. Its reset value

is logic zero. Before the IPR can be modified by 4-

bit write instructions, all interrupts must first be

disabled by a DI instruction.

By manipulating the IPR settings, you can choose to

process all interrupt requests with the same priority

level, or you can select one type of interrupt for

high-priority processing. A low-priority interrupt can

itself be interrupted by a high-priority interrupt, but

not by another low-priority interrupt. A high-priority

interrupt cannot be interrupted by any other interrupt

source.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KS57C2916 | 4-BIT CMOS Microcontroller(4位微控制器) |

| KS57P2916 | 4-BIT CMOS Microcontroller(4位微控制器) |

| KS57C5312 | The KS57C5204/C5208/C5304/C5308/C5312 single-chip CMOS microcontroller has been designed for highperformance using SAM 47 Samsung Arrangeable Microcon |

| KS57P5312 | The KS57C5204/C5208/C5304/C5308/C5312 single-chip CMOS microcontroller has been designed for highperformance using SAM 47 Samsung Arrangeable Microcon |

| KS57C5404 | 4-BIT CMOS Microcontroller(4位微控制器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KS57C2916 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:The KS57C2916 single-chip CMOS microcontroller has been designed for high performance using Samsungs newest 4-bit CPU core, SAM47 (Samsung Arrangeable |

| KS57C3016 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:4-BIT CMOS MICROCONTROLLER |

| KS57C3204 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:The KS57C3204 single-chip CMOS microcontroller has been designed for high performance using Samsungs newest 4-bit CPU core, SAM47 (Samsung Arrangeable |

| KS57C3316 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:The KS57C3316 single-chip CMOS microcontroller has been designed for high performance using Samsungs newest 4-bit CPU core, SAM47 (Samsung Arrangeable |

| KS57C4104 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:The KS57C4104/KS57C4204/KS57C4304 single-chip CMOS microcontroller has been designed for very high performance using Samsungs newest 4-bit CPU core, S |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。