- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367612 > LU6612-T64-DB LU6612 FASTCAT TM Single-FET for 10Base-T/100Base-TX PDF資料下載

參數(shù)資料

| 型號(hào): | LU6612-T64-DB |

| 英文描述: | LU6612 FASTCAT TM Single-FET for 10Base-T/100Base-TX |

| 中文描述: | LU6612 FASTCAT商標(biāo)單的10BASE-T/100BASE-TX快速以太網(wǎng)場(chǎng)效應(yīng)管 |

| 文件頁(yè)數(shù): | 11/36頁(yè) |

| 文件大?。?/td> | 528K |

| 代理商: | LU6612-T64-DB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

Lucent Technologies Inc.

11

Data Sheet

July 2000

LU6612

FASTCAT Single-FET for 10Base-T/100Base-TX

Pin Information

(continued)

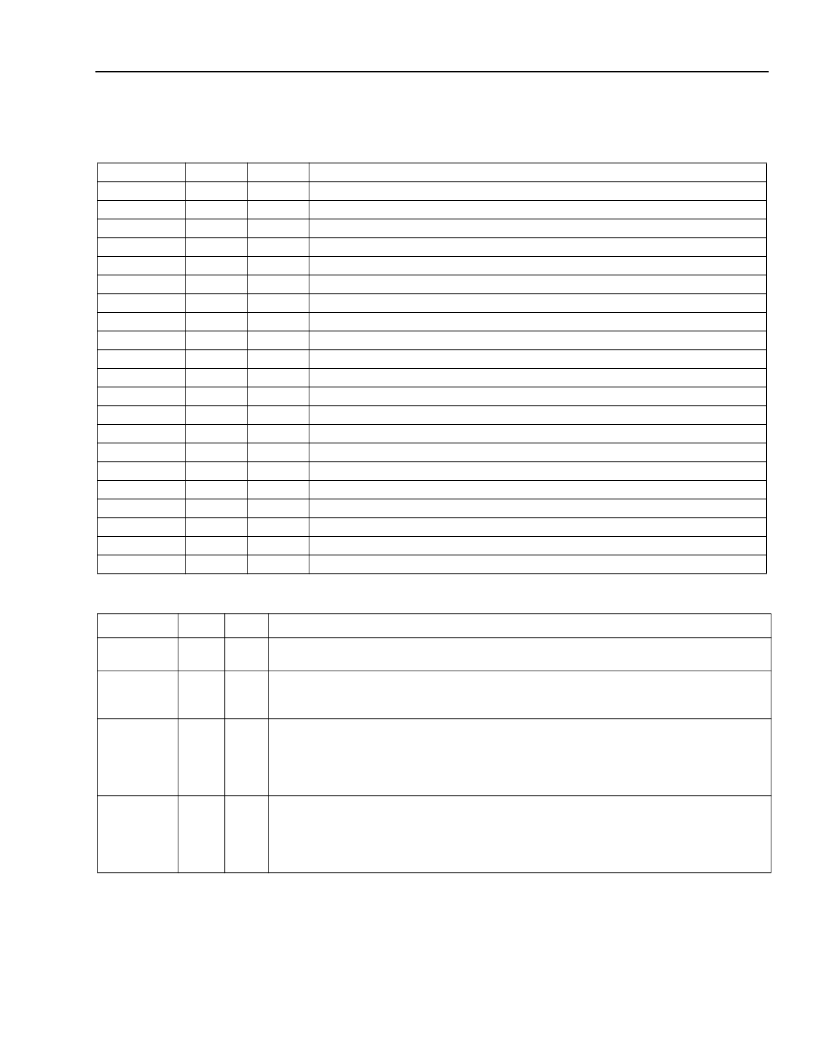

Table 4. Ground and Power Pins (21)

Table 5. Miscellaneous Pins (20)

*

↑

indicates there is an internal pull-up;

↓

indicates there is an internal pull-down.

Signal

V

CC

IOA

GNDIOA

V

CC

IOB

GNDIOB

GNDIOC

V

CC

DIGA

GNDDIGA

V

CC

DIGB

GNDDIGB

V

CC

REC

GNDREC

V

CC

PLL

GNDPLL

V

CC

T

GNDT

V

CC

EQAP

GNDEQAP

V

CC

BG

GNDBG

V

CC

BT

GNDBT

Type

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

Pin

6

7

54

53

41

35

36

49

48

60

59

20

23

11

10

61

64

1

3

14

13

Description

Digital +5 V power supply for I/O

Digital ground for I/O

Digital +5 V power supply for I/O

Digital ground for I/O

Digital ground for I/O

Digital +5 V power supply for logic

Digital ground for logic

Digital +5 V power supply for logic

Digital ground for logic

Digital +5 V power supply for clock recovery circuit

Digital ground for clock recovery circuit

Analog +5 V power supply for 10 MHz and 100 MHz PLL clock synthesizer

Analog ground for 10 MHz and 100 MHz PLL clock synthesizer

Analog +5 V power supply for transmitter

Analog ground for transmitter

Analog +5 V power supply for equalizer and adaptation circuit

Analog ground for adaptation circuit.

Analog +5 V power supply for band-gap circuit

Analog ground band-gap circuit

Analog +5 V power supply for 10Base-T transmitter

Analog ground for 10Base-T transmitter

Signal

LSCLK1

Type

*

I

Pin

21

Description

Local Symbol Clock.

25 MHz clock,

±

100 ppm, 40%—60% duty cycle. This input is

connected to one terminal of a 25 MHz crystal or an external 25 MHz clock source.

Local Symbol Clock.

25 MHz crystal feedback. This output is connected to the

other terminal of a 25 MHz crystal or an external 25 MHz. If LSCLK1 is driven from

an external clock source, LSCLK2 is left unconnected.

Link LED.

This pin indicates good link status. At powerup/reset, this pin is sampled

as input and to set the PHYAD[0] bit. If pulled high through a resistor, this pin will set

PHYAD[0] to a high or if pulled low through a resistor, will set PHYAD[0] to a zero.

When this pin is pulled high the LED output will be active-low, when pulled low the

LED output will be active-high.

Activity LED.

This pin indicates transmit/receive activity. At powerup/reset, this pin

is sampled as input to set the PHYAD[1] bit. If pulled high through a resistor, this pin

will set PHYAD[1] to a high or if pulled low through a resistor, will set PHYAD[1] to a

zero. When this pin is pulled high the LED output will be active-low, when pulled low

the LED output will be active-high.

LSCLK2

O

22

LINKLED/

PHYAD[0]

I/O

4

ACTLED/

PHYAD[1]

I/O

5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LU6612 | Single-FET for 10Base-T/100Base-TX(應(yīng)用于10基數(shù)-T和100基數(shù)-TX 的單快速以太網(wǎng)收發(fā)器) |

| LU6X14FT | Telecommunication IC |

| LU97 | Telecommunication IC |

| LUC3X01 | LAN Transceiver |

| LUCDA4044 | Phase Frequency Detector |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LU67 | 制造商:Thomas & Betts 功能描述:2 CONDUIT BODY,GRAY IRON,LU,F-7 |

| LU670Z | 制造商:SEOUL 制造商全稱:Seoul Semiconductor 功能描述:GREEN OVAL LAMP LED |

| LU671 | 制造商:SEOUL 制造商全稱:Seoul Semiconductor 功能描述:RED OVAL LAMP LED |

| LU680Z | 制造商:SEOUL 制造商全稱:Seoul Semiconductor 功能描述:GREEN OVAL LAMP LED |

| LU681 | 制造商:SEOUL 制造商全稱:Seoul Semiconductor 功能描述:BLUE OVAL LAMP LED |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。