- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377798 > LXT351QE (INTEL CORP) PCM TRANSCEIVER|SINGLE|CEPT PCM-30/E-1|CMOS|QFP|44PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號(hào): | LXT351QE |

| 廠商: | INTEL CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | PCM TRANSCEIVER|SINGLE|CEPT PCM-30/E-1|CMOS|QFP|44PIN|PLASTIC |

| 中文描述: | DATACOM, PCM TRANSCEIVER, PQFP44 |

| 封裝: | PLASTIC, QFP-44 |

| 文件頁(yè)數(shù): | 26/46頁(yè) |

| 文件大?。?/td> | 1132K |

| 代理商: | LXT351QE |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)當(dāng)前第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)

LXT351

—

T1/E1 Short Haul Transceiver with Crystal-less Jitter Attenuation

26

Datasheet

4

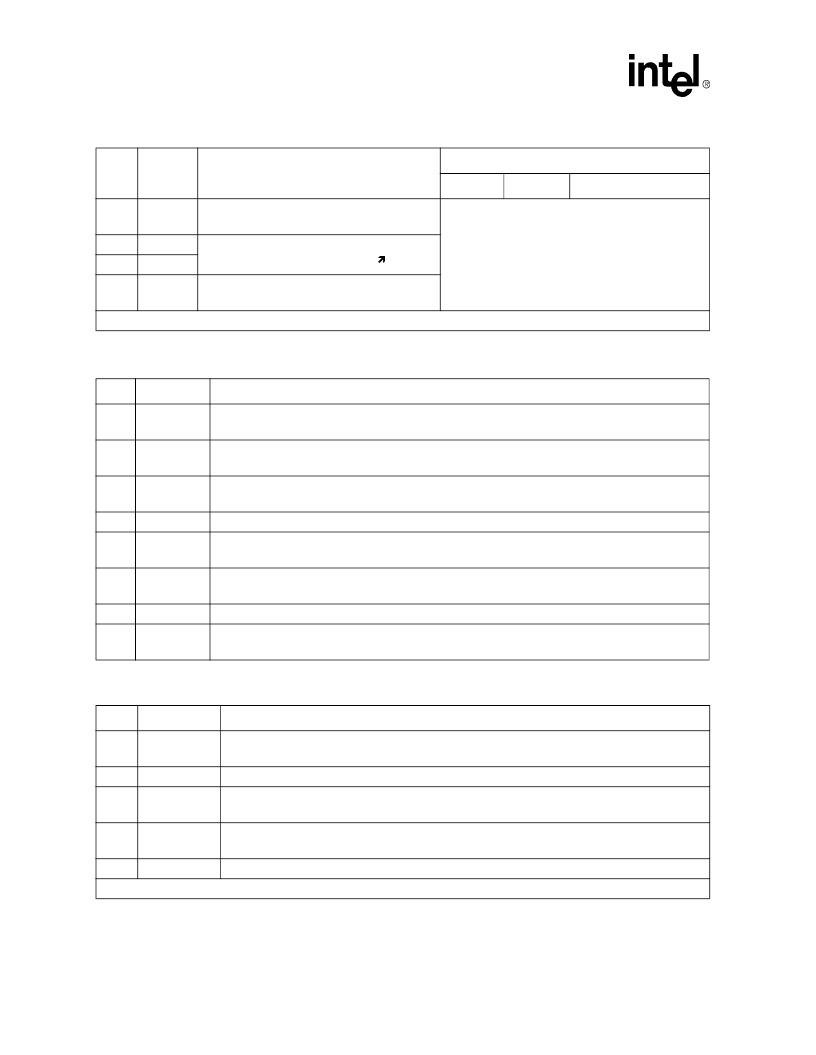

ETAOS

1 = Enable Transmit All Ones

0 = Disable Transmit All Ones

5

EPAT0

Selects internal data pattern transmission. See

right hand section of table for codes.

6

EPAT1

7

RESET

1 = Reset device states and clear all registers.

0 = Reset complete.

Table 10. Control Register #3

Read/Write, Address (A7-A0) = x010010x

Bit

Name

Description

0

ESJAM

1 = Disable jamming of Elastic Store read out clock (

1

/

8

bit-time adjustment for over/underflow).

0 = Enable jamming of Elastic Store read out clock

1

ESCEN

1 = Center ES pointer for a difference of 16 or 32, depending on depth (clears automatically).

0 = Centering completed

2

ES64

1 = Set elastic store depth to 64 bits.

0 = Set elastic store depth to 32 bits.

3

-

Reserved. Set to 0 for normal operation.

4

EQZMON

1 = Configure receiver equalizer for monitor mode application (DSX-1 monitor).

0 = Configure receiver equalizer for normal mode application

5

SBIST

1 = Start Built-In Self Test.

0 = Built-In Self Test complete.

6

-

Reserved. Set to 0 for normal operation.

7

JA6HZ

1 = Set bandwidth of jitter attenuation loop to 6 Hz.

0 = Set bandwidth of jitter attenuation loop to 3 Hz.

Table 11. Interrupt Clear Register

Read/Write, Address (A7-A0) = x010011x

Bit

Name

Function

1

0

CLOS

1 = Clear/Mask Loss of Signal interrupt.

0 = Enable Loss of Signal interrupt.

1

-

Reserved. Set to 1 for normal operation.

2

CAIS

1 = Clear/Mask Alarm Indication Signal interrupt.

0 = Enable Alarm Indication Signal interrupt.

3

CQRSS

1 = Clear/Mask Quasi-Random Signal Source interrupt.

0 = Enable Quasi-Random Signal Source interrupt.

4

-

Reserved. Set to 1 for normal operation.

1. Leaving a 1 of in any of these bits masks the associated interrupt.

Table 9. Control Register #2

Read/Write, Address (A7-A0) = x010001x

Bit

Name

Function

Pattern

EPAT0

EPAT1

Selected

1. To enable Dual loopback (DLOOP), set both ERLOOP = 1 and ELLOOP = 1.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT361QE | Integrated T1/E1 LH/SH Transceivers for DS1/DSX-1/CSU or NTU/ISDN PRI Applications |

| LXT360 | Integrated T1/E1 LH/SH Transceivers for DS1/DSX-1/CSU or NTU/ISDN PRI Applications |

| LXT361 | Integrated T1/E1 LH/SH Transceivers for DS1/DSX-1/CSU or NTU/ISDN PRI Applications |

| LXT360QE | CONNECTOR ACCESSORY |

| LXT381BE | Octal E1 Line Interface Unit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT360 | 制造商:LVL1 制造商全稱:LVL1 功能描述:Integrated T1/E1 LH/SH Transceivers for DS1/DSX-1/CSU or NTU/ISDN PRI Applications |

| LXT360LE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM TRANSCEIVER|SINGLE|CEPT PCM-30/E-1|CMOS|QFP|44PIN|PLASTIC |

| LXT360PE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM TRANSCEIVER|SINGLE|CEPT PCM-30/E-1|CMOS|LDCC|28PIN|PLASTIC |

| LXT360QE | 制造商:Intel 功能描述: 制造商:LEVEL ONE 功能描述: |

| LXT361 | 制造商:LVL1 制造商全稱:LVL1 功能描述:Integrated T1/E1 LH/SH Transceivers for DS1/DSX-1/CSU or NTU/ISDN PRI Applications |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。